Other Parts Discussed in Thread: CDC6C, LMH1983

Tool/software:

Hi,

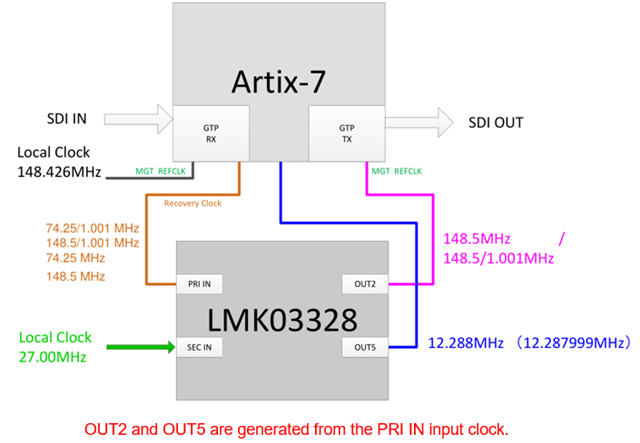

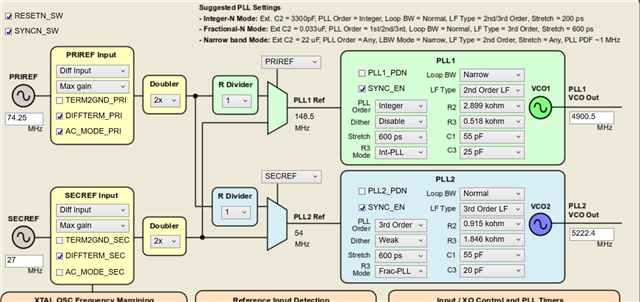

We are currently considering using your device LMK03328 in combination with Xilinx Artix-7 FPGA.

The system is intended to operate as follows:

-

Input clock (recovered clock): 74.25MHz, 74.25/1.001MHz, 148.5MHz, 148.5/1.001MHz

-

LMK03328 is used for jitter cleaning and clock generation. The output clocks are:

-

148.5MHz or 148.5/1.001MHz (used as REFCLK for Artix-7 GTP transmitter)

-

12.288MHz (for audio clock)

-

We are aware that the GTP transceivers on Artix-7 have stringent phase noise / jitter mask requirements for the REFCLK.

Could you please confirm whether there are any concerns or limitations when using LMK03328 in this configuration?

Particularly, we would like your opinion on whether the jitter performance of the 148.5MHz (or 148.5/1.001MHz) output is suitable to meet the GTP transceiver’s REFCLK requirement.

Best regards,

Conor