Part Number: LMK04832

Tool/software:

Hi,TI Team:

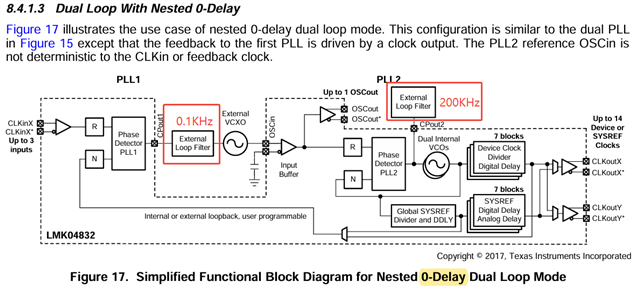

I would like to know the detailed locking process of PLL1/2 in Nested 0-Delay Dual Loop Mode.

How long does it take for PLL1/2 to lock (the loop filter bandwidth is shown in the figure)?

During the locking process, does the chip have any output, and does the output divider take effect?

Thanks!