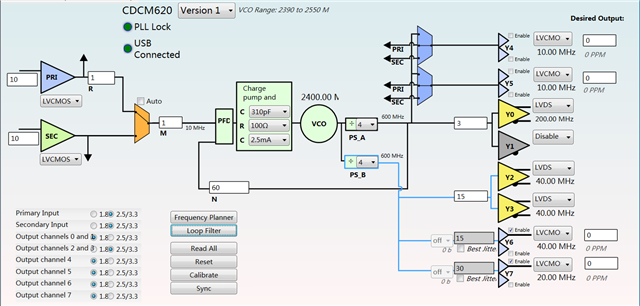

Tool/software:

We used the CDCM6208 on our board, locked to a 10M source, outputting 40M.

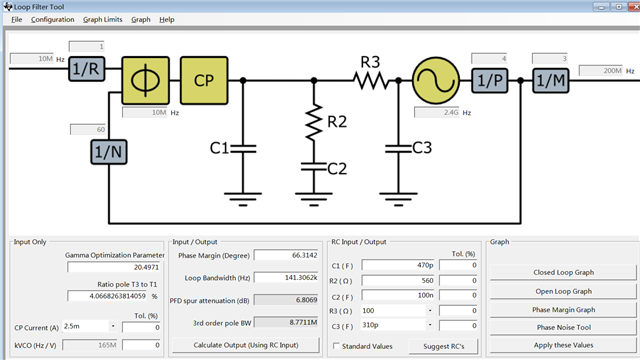

We are currently facing a problem. In some cases, the phase noise of the clock source is not very clean. There is significant noise at 10K. We would like to reduce the bandwidth from 140K to a smaller value. We have tried many parameters ourselves, but the results are not good. Could you help us take a look and suggest a configuration?