Tool/software:

Hello,

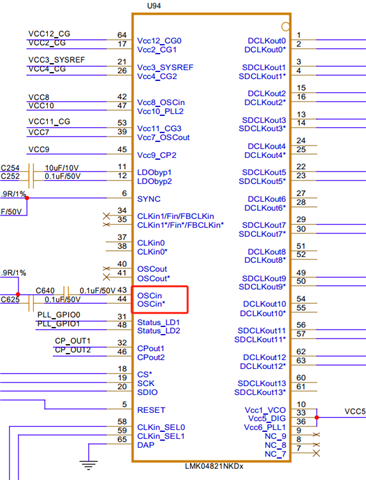

The customer wants to achieve phase synchronization of the LMK04828 output clock between multiple boards, but the phase always changes randomly.

Synchronization scheme (status): The 125M input is provided by another module on each board, and the modules are connected through switches to ensure that the 125M reference clock input is from the same source and synchronized; Our solution for synchronization between multiple boards is to send a pulse through the sync pin to achieve synchronization. The specific method is to send a trigger signal to both boards simultaneously through an external signal source. When this signal is detected by the FPGA, a enable is raised. During the effective period of the enable, when the 1pps signal sent by the 125M clock module is detected, the two signals are in phase with each other in the logic, and the new signal after it is used as the synchronization event of 04828 in the multiple boards (the accuracy of the synchronization event cannot reach ps level)

Our main concern now is to know if our current solution is feasible. If so, at what stage should the sync signal be given and how should the registers be configured?

I have now tried and found that when I give the sync signal, I observed the sysref signal output by 04828 on two boards through an oscilloscope and found that there was no action. Therefore, I am not sure if our solution is not feasible or if there is a problem during the configuration process. I would like to ask for guidance on this matter.