Part Number: CDCM7005

Hello,

Our customer has some application question how CDCM7005 works.

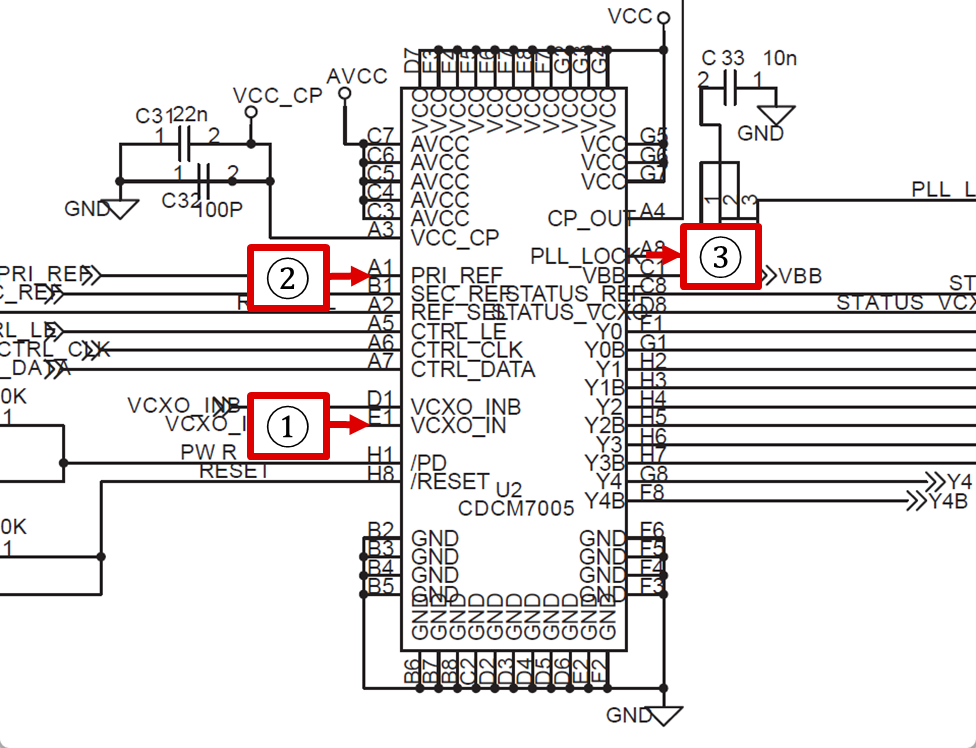

Q-1 : In case (2) PRI_REF is not locked while (1) VCXO_IN clock comes in, (3) PLL_LOCK output High level ?

Q-2 : While the customer swich over PRI_REF clock to other clock by via external circuitry, doe he need to input reset signal via REST/HOLD pin ?

Q-3 : unless he reset in above Q-2, does PLL_LOCK go to High ouput ?

best regards,