Part Number: LMK05028

Other Parts Discussed in Thread: LMK00804B

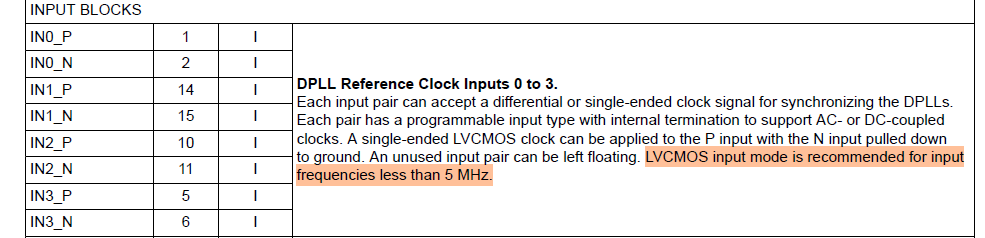

We want to connect to VSC8512 PHY recoverd clock(125MHz) to PLL(LMK05028) Input which is LVCMOS, But according to the snippet attached LMK05028 Datasheet is saying that LVCMOS can take only less than 5MHz. So please tell us this will work or not? If it works do we need any specific termination for it?

Thanks & Regards,

J Shashikanth Reddy