Other Parts Discussed in Thread: CDCM6208

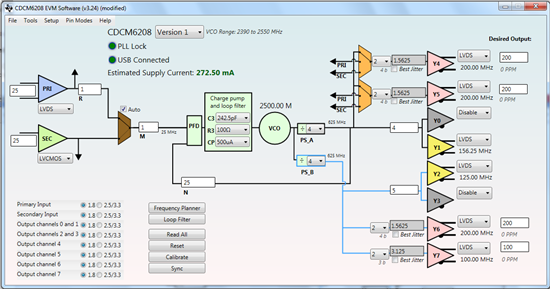

Looking for a clock generator to support below needed clocks:

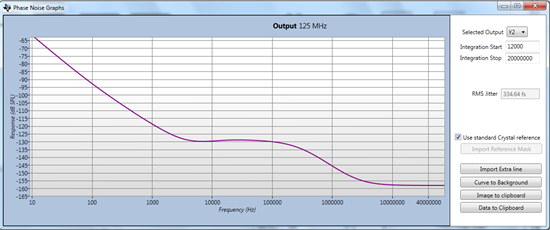

1x LVDS - 125MHz for QSGMII (low phase noise < 1ps),

1x LVDS - 125Mhz for Marvell PHY.

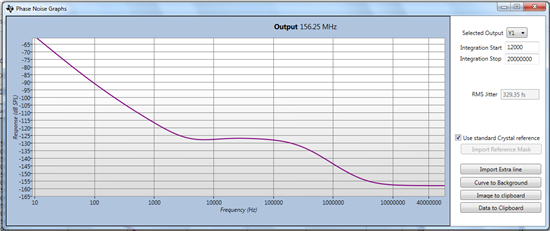

1x LVDS - 156.25MHz for 10GBASE-T (Xilinx Serdes)

3x LVDS - 200Mhz (DDR Clock & system Clock for FPGA)

The 125Mhz and 156.25MHz jitter mask is attached below: