Hi e2e-ers,

I'm designing a JESD204B synthesis/acquisition system, and trying to synchronize JESD204B DACs and ADCs across different converters and across multiple boards. This seems to be a common question -- here are related links to show I've done some homework:

- Multiple LMK04828 Synchronization??

- LMK04828 - Multiple LMK's and Multiple JESD204B ADCs synchronization

- LMK04828: Deterministic timing using SYNC

We're still finding the LMK04828 datasheet tough to parse precisely.

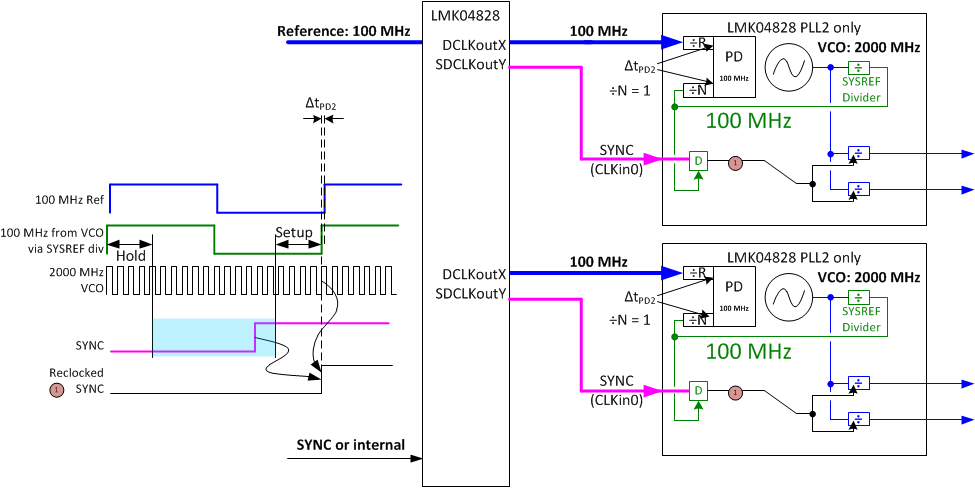

Our board-to-board clock distribution starts with a slow clock (~10 MHz) and an accompanying (synchronous) sync pulse. This clock and sync signal are fanned out to multiple LMK04828s to drive clock and SYSREF signals on many JESD204B ADCs and DACs. Following the advice linked above, we're planning on using the LMKs in Cascaded 0-Delay mode.

Is it possible to ensure the ADCs/DACs receive SYSREF pulses on the same O(1 GHz) clock edge in this scenario?

There are some hints in the datasheet (9.3.2.1.1: Setup of SYSREF Example), where SYNC is applied in two different configurations:

- The first SYNC pulse resets internal dividers within the LMK04828. This pulse needs to be consistent between LMK04828s. How can we configure two LMKs to accept this SYNC pulse synchronous to their input clocks? (If not, is there some other way to get consistent divider resets?)

- The second SYNC pulse triggers the pulser to reset downstream JESD204B devices. Can you confirm that this SYNC is synchronous to CLKinX when in Cascaded 0-delay mode? (If not, is there some other way to get consistent SYSREF pulses?)

Finally, when SYNC is used synchronously to an input clock, it has some setup/hold requirements -- and there are none in the datasheet. Any suggestions?

That's a bunch of questions jammed into a short amount of text -- thanks in advance for responding.

best,

Graeme