Other Parts Discussed in Thread: CDCE62005, DAC3484, CDCM7005

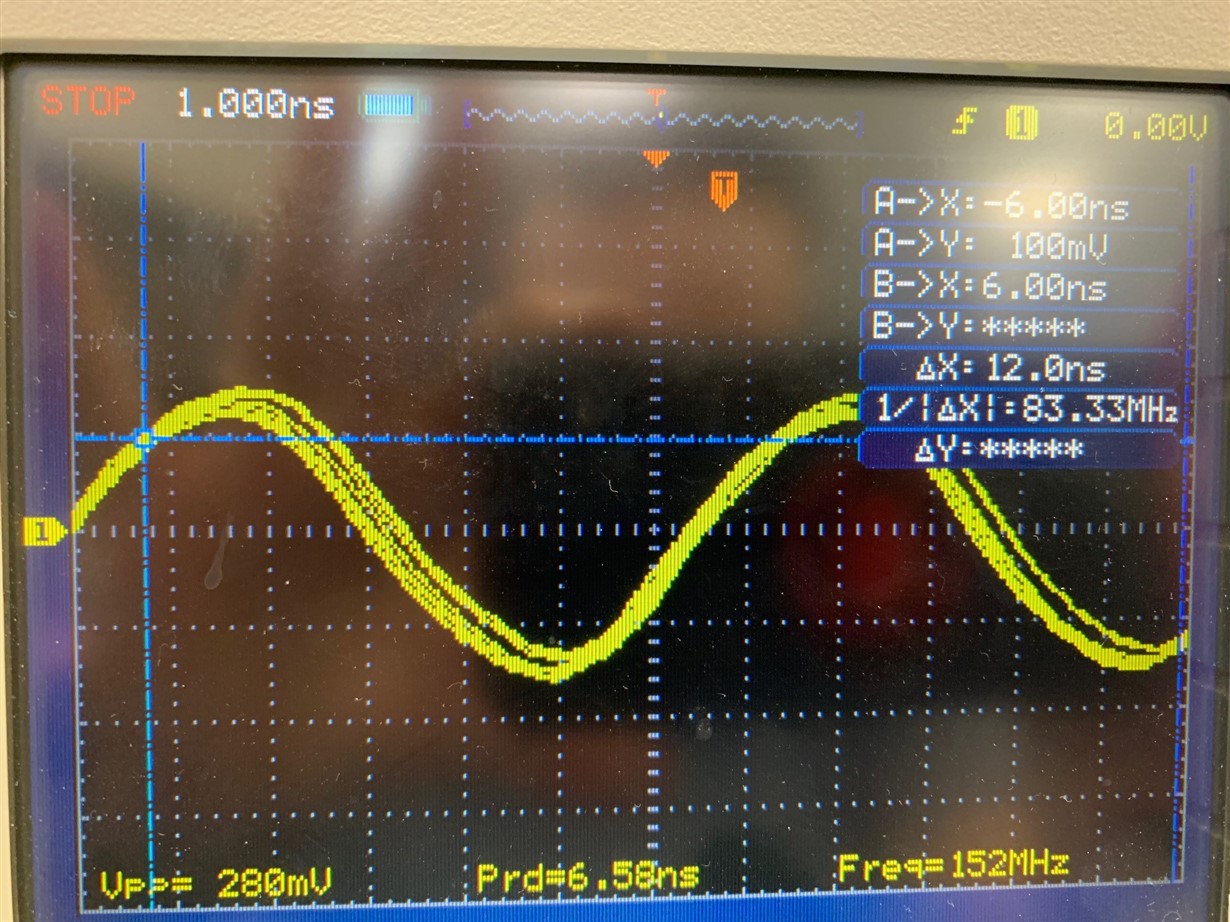

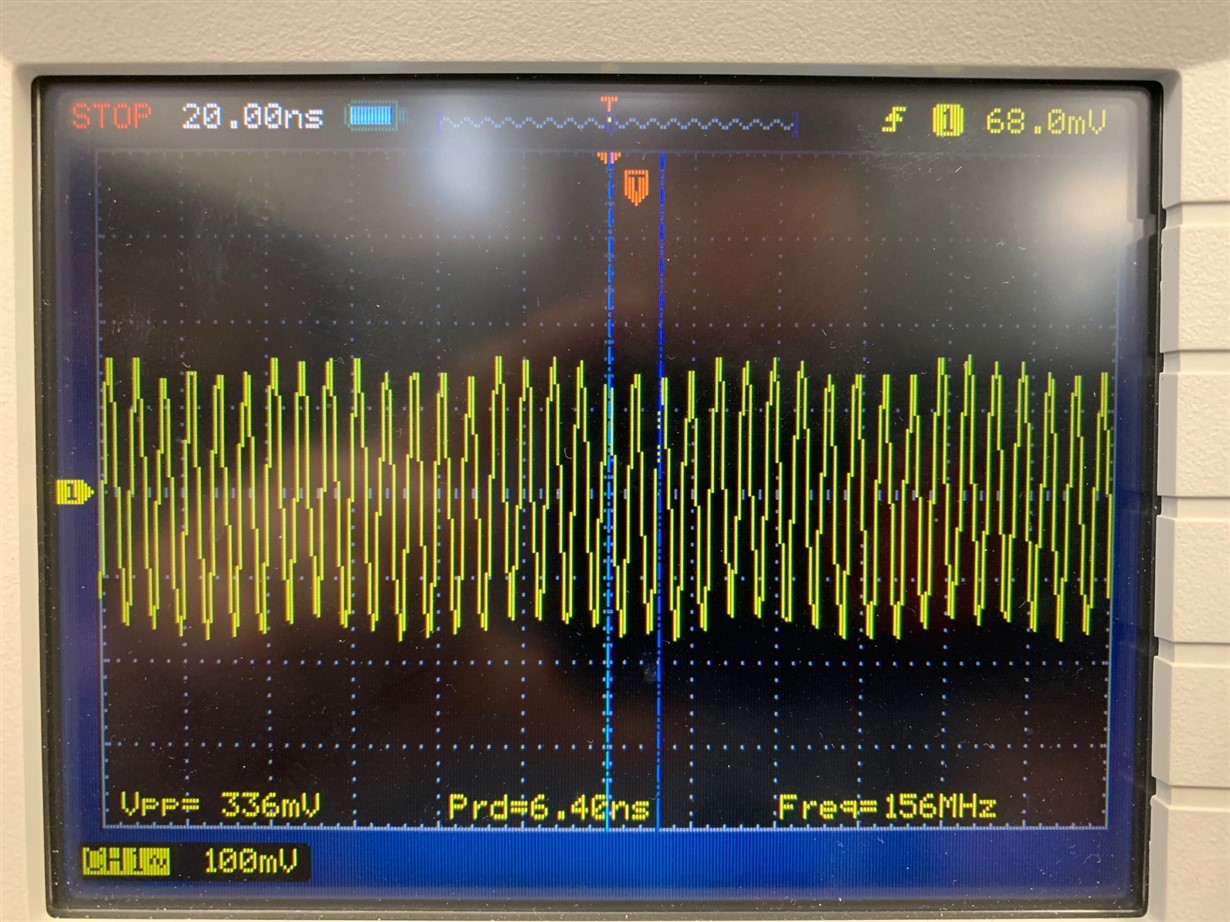

I'm driving out 1 1Vpp 153.6MHz LVPECL20 +/- signal from CLKout0/CLKout0* and connected to a ADC-WB-BB balun that connects to the J9 CLKIN input of the DAC3484EVM. The signal gets attentuated to a 24mVpp signal riding on a 200mV DC bias to the on-board CDCE62005 PRI REF+ input. I don't believe that this external clock is making it through the clock chip to provide a clock output back to the FPGA. The output is 2.72VDC on both FPGA_CLKOUTP and FPGA_CLKOUTN. I've attachecd the DAC3484EVM register setup file.

x00 x089C x01 x050E x02 xF002 x03 xF000 x04 x4068 x05 x3B60 x06 x2500 x07 xFFFF x08 x0000 x09 x8000 x0A x0000 x0B x0000 x0C x0400 x0D x0400 x0E x0400 x0F x0400 x10 x0000 x11 x0000 x12 x0000 x13 x0000 x14 x0000 x15 x0000 x16 x0000 x17 x0000 x18 x280F x19 x0840 x1A x0030 x1B x0800 x1C x0000 x1D x0000 x1E x1111 x1F x1182 x20 x2400 x22 x1B1F x23 x07FF x24 x0000 x25 x7A78 x26 xB6B6 x27 xEAEA x28 x4545 x29 x1A1A x2A x1616 x2B xAAAA x2C xC6C6 x2D x0004 x2E x0000 x2F x0000 x30 x0000 x7F x0004 CDCE62005 Registers Freq:0.000000MHz Address Data 00 00400000 01 80040001 02 81800002 03 81040003 04 00040004 05 01281A65 06 04BE3F76 07 170037F7 08 20001808