Other Parts Discussed in Thread: DAC38RF82EVM, DAC38RF82,

Hi there,

I am using a DAC38RF82EVM in combination with a TSW14J56EVM to run an optical experiment in which I want to synchronize the output data stream (8.84736Gsps) out of my dac (set according the configuration given below), to an external clock source given by the trigger of my pulsed laser which is running at 80.028MHz:

DAC38RF82_8847p36MSPS_PLL_8bitsmode_VCXO.cfg

My idea was to use a nested 0-delay dual loop to achieve fixed phase relationship between clkin1 (the 80.082 Mhz source of the pulsed laser) and the digital data at 8.84736Gsps converted by the dac.

According to the parameters that i am setting I get PLL1 LD and PLL2 LD turning green (the LD switches off when I unplug the laser clock off SMA J4). Therefore, I assume both PLL are locked and all clocks are in phase. Especially the dac sampling clock at 8.84736Gsps is in phase with my laser clock.

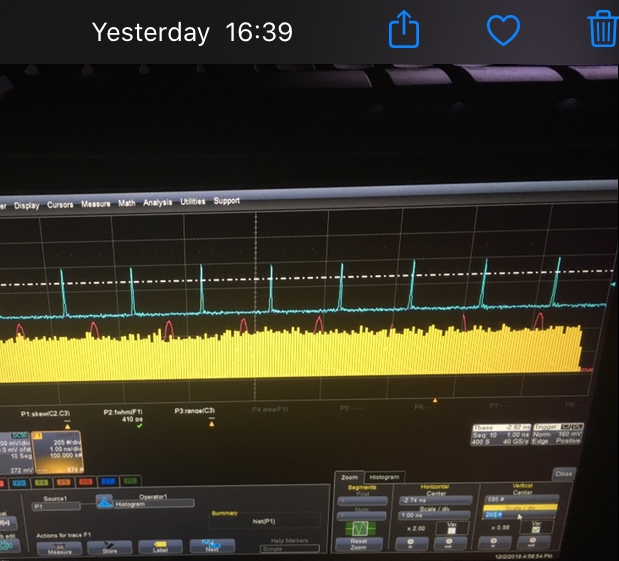

At this stage i generate a waveform which i send to a fast scope together with the laser clock. I would expect that, if locking is working correctly, the two pulses travel together but when i trigger on laser clock i see the generated waveform fluctuating back and forth.

Can you help with this please? Can you suggest which settings I shall use in the GUI?

Thanks

Antonio