Dear Specialists,

My customer is confirming ADC3221EVM and has a question.

I would be grateful if you could advise.

---

We're confirming ADC3221EVM

The register value of ADC3221EVM was read using ADC3000_GUI.

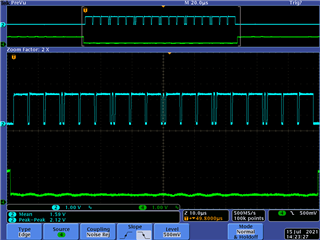

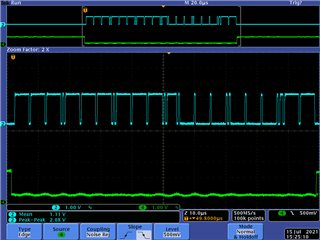

At that time, when I checked the clock (SCLK) during read operation with the USB output signal, it was only 23 clocks, not 24 clocks in the data sheet described.

23 clocks are no problem, or 23 clocks are spec?

(There are 24 clocks during register write operation)

Could you please see attached the waveform.

ADC3221 register writing and reading waveform .pptx

---

I appreciate your great help in advance.

Best regards,

Shinichi