Other Parts Discussed in Thread: LMK04828

Hi,

We have ordered the Eval board DAC39J82EVM and have started the characterization.

We are trying to measure NSD in our LAB, but we are unable to meet the numbers due to equipment limitations.

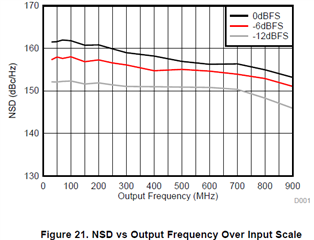

Since this is an important parameter in our design, we would like to know the measurement setup used for validating the NSD numbers mentioned in the DAC datasheet (Figure 21, Page no 21). Could you please provide the measurement setup and parameters used? NSD figure from Datasheet is attached below for reference

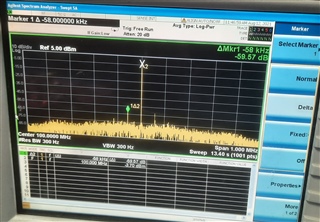

Another observation with DAC39J82EVM is while generating any output from the DAC, Spurious components are observed on both sides of Generated output at around 58-60 KHz offset frequency. These Spurious components are seen even when DAC is configured to generate LO output only (FPGA board is powered off and DAC generates LO @ 100 MHz). Are you aware of these spurious components and how to get rid of them? A Reference Snapshot is attached below.

Thanks,

Kiran