Hi,

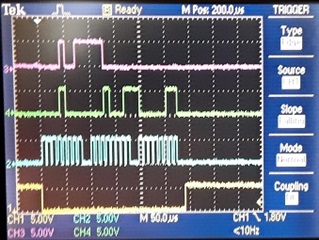

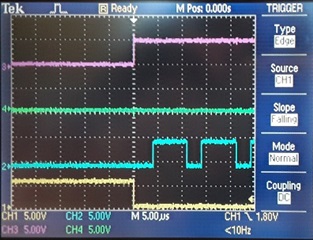

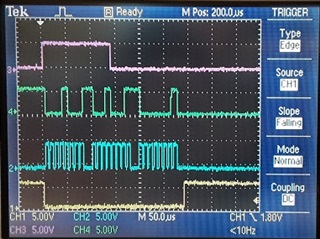

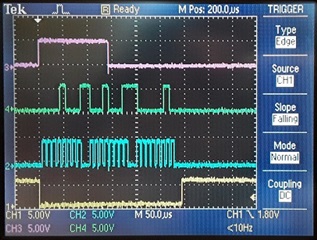

I'm just starting to work with the ADS7038. I'm currently trying to read all 8 inputs using the manual mode, but it looks like the chip just keeps sending the same value from analog 0 and does not advance to read any other analog point.

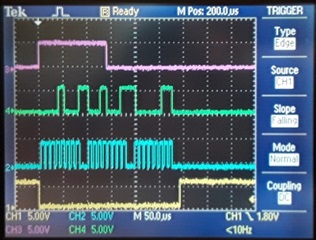

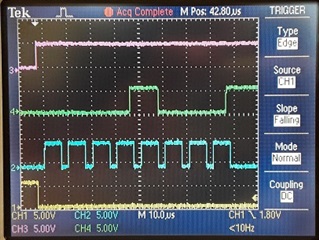

I'm talking to the ADS7038 over the SPI port and I'm confident that the interface is working because I can write to a register and read it back successfully.

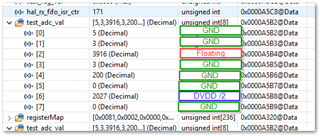

For testing the manual mode, it looks like all of the initial settings (CONV_MODE=00, SEQ_MODE=00, & PIN_CFG=0 from page 23 in the ADS7038 datasheet) are their default values, so I didn't change any of them. Then I gave the ADS7038 these 3 commands to see if I could read the first 3 analog inputs (write to the CHANNEL_SEL register, Address=0x11):

08, 11, 01; set MANUAL_CHID to 1 for the next read

08, 11, 02; set MANUAL_CHID to 2 for the next read

08, 11, 03; set MANUAL_CHID to 3 for the next read

In each case when I look at the data that was received, it looks like it just keeps reading analog 0 as I mentioned above.

Can anyone me what I'm doing wrong and what I can do to fix it?

Thank you for your response.

Brad McMillan