Other Parts Discussed in Thread: LMX2594, LMX2572

We are using ADC12DJ3200 operated in JMODE 2 for 3.2 GSPS.

GTH refclk (120 MHz) for FPGA generated from LMX2572 and ADC sampling clock generated (800MHz) from LMX2594.

1.The order and value of adc12dj3200 register configuration are as follows:

`define CONFIG_A_SOFT_RESET 24'h00_00B0;// `define JESD_EN_DISABLE 24'h02_0000;// `define CAL_EN_DISABLE 24'h00_6100;// `define JTEST_RAMP 24'h02_0504;//RAMP TESTMODE `define JESD204B_JMODE2 24'h02_0102;//JMODE=2,12bit `define JESD204B_K_3 24'h02_021F;// `define JESD204B_CONTROL 24'h02_0400; `define CAL_CFG0 24'h00_6201; `define CAL_EN_ENABLE 24'h00_6101; `define JESD_EN_ENABLE 24'h02_0001; //wait for SYNC change `define CAL_SOFT_TRIG_0 24'h00_6C00; `define CAL_SOFT_TRIG_1 24'h00_6C01;

Also,we have read out the configured register and it is correct.

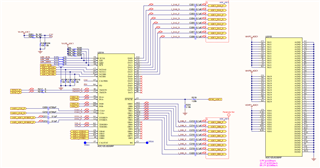

2.schematic diagram is as follow:

3.Simulation generate input clock,and connect the TX port and RX port of Ti_ 204C_IP .Through simulation, the CGS can be completed normally.