Hi,

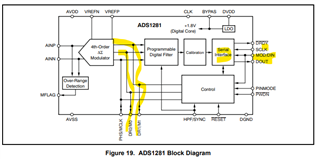

Catalog Number - ADS1281PWR.

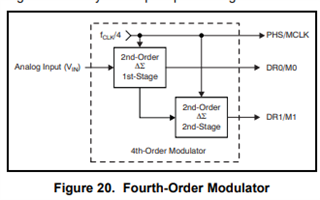

I can't use SPI communication lines so I connect the M0 and M1 Inputs ports to the FPGA.

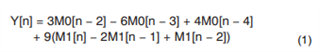

Within the FPGA I compute the Y[n] function and get results in the range of -24 to +25.

When I only used input M0, I knew how to correctly calculate the analog value at the ADC input.

But now, I do not know how to "correctly" treat the values I get from Y[n]. Do I have to constantly sum up the last 32 results of Y[n]?

Thanks.