Other Parts Discussed in Thread: LMH6554, ADC3664, ADS62P44, ADS62P43, ADC16DV160

Hello,

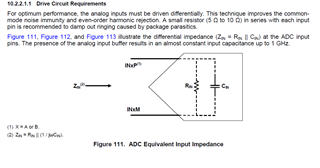

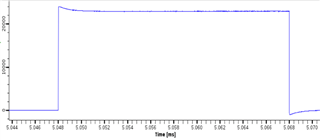

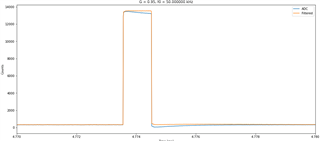

We purchased a DC-coupled, single-ended ADC card with a ADS42JB69 ADC that is being driven by a LMH6554. The ADC driver circuit follows the typical application schematic on the LMH6554 datasheet, minus the AC coupling caps. When we apply a square pulse we get droop on the top of the pulse and undershoot when the pulse ends, as if something is AC coupled. Can the ADC be driven in this DC-coupled configuration?

Thanks,

Trent