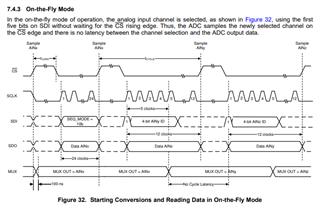

Looking at Figure 32 (On-the-Fly Mode), I am having trouble understanding the timing relationship between CS and acquisition/conversion.

My understanding is that conversion begins at the rising edge of CS, and that conversion data cannot be read (i.e. SCLK must remain inactive) for tCONV=600ns after this rising edge. Then, 5 SCLK periods are required to select the next channel -- at 60 MHz this is 83ns. If acquisition begins immediately after this fifth SCLK, then an additional tACQ=400ns must pass before the next CS rising edge. Given this, it looks like the minimum conversion period is 600+84+400 = 1083ns. Am I misunderstanding something? Is there a way to achieve a 1000ns conversion period using On-the-Fly Mode?

Thank you,

Jonathan