Other Parts Discussed in Thread: ADS7040

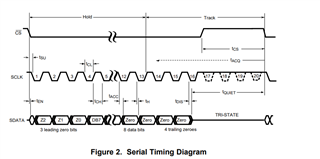

The datasheet states that the sample is aborted "if CS is brought high after the 10th falling edge, but before the 16th falling edge," however the implications of this on the timing of the next /CS falling edge are not addressed. On what edge is an abort recognized, and does the device immediately return to Track mode when this happens, or is it expected that clocking continues and that Track mode is still entered normally after 12.5 clocks?

Put another way, is the minimum time between falling edges of /CS at all impacted at all by an abort, provided clocking continues?

For the curious, this is not a performance optimization question. Rather, I'm constructing some minimalist logic to read out a serial ADC and would like the result to be compatible with as many inexpensive 8-bit ADCs as possible (other likely candidates being the ADS7029 and ADS7040). The 16-cycle 1-MHz scenario described in the Throughput section is quite attractive for my purpose, however due to the extreme scarcity of hardware resources, the exact duration of /CS requires some careful budgeting. My hope would be that the 16-cycle 1-MHz frame timing holds, regardless of whether the sample is "aborted" immediately after DB7 is output.

Very best,

Aaron