Other Parts Discussed in Thread: DAC39J84

Hi, I downloaded TI-JESD204B IP and use zc706_8b10b ref design for VC707 fpga board and DAC39j84. I use LMFS=8411 and HD=1. Here are few questions that bug me during my implementation:

1. the ref design does not have sysref input, so do we need sysref input if we only connect one DAC39j84 board? Does it mean if we don't use multi DAC board, we don't need sysref signal? Or we need to add sysref in real design?

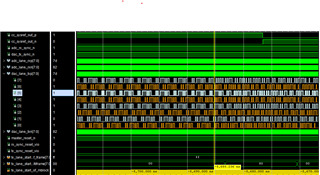

2. My design is not working, and when I checked the ILA, I found that tx_lane_start_of_frame is 1 but tx_lane_start_of_multiframe is 0. Does that mean there's something wrong in my design? I'm kind of confused about this part.

3. We won't have ILAS process for tx if cfg_tx_ilas_test_mode=0 right? If it's 1, whst is the ILAS series? Is it 4 byte from K28.0 to K28.3?

4. I suffered timing failure meanly between clkout0 and sys_clk_sys_pll1 during setup period, will this be a problem for the design?

Thanks advance for your help.

Best,

Shuyi