I am trying to use my evaluation boards together for the PIC and the ADS, so that I can show communication and reading of ADC channel readings. As for the configuration between the two...

1. I have the PIC eval board wired to the EVM for signals, SCLK, DIN, DOUT, CS, DRDY, SYNC/RST. I have wires on J6 going between the boards.

2. I do not have the PHI board connected.

3. Using a 3.3V external supply applied to test points AVDD and DVDD on the EVM.

4. The jumper is removed on JP9 for the LDO/MSP selection.

5. I did not remove R45.

On the scope I verified the signals when writing (CS, SCLK @ 1MHz, DIN) lines are correctly outputting to the ADS. When I look at DOUT, the output is not clean. Only seeing noise where the SCLK and DIN is present. Never reaching 3.3V and having a proper pulse width. The pulses expecting the returned data are not there; just seems like noise spikes (very thin and never reaching 3.3V).

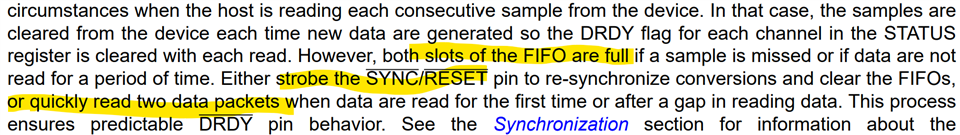

DRDY never reaches 0V, it hovers around half a volt most of the time with blimps at around 4kHz. This is seen no matter if the channels are enabled or disabled. I thought DRDY is to be high. On the PIC I make sure it is latched high. What could be causing this behavior?

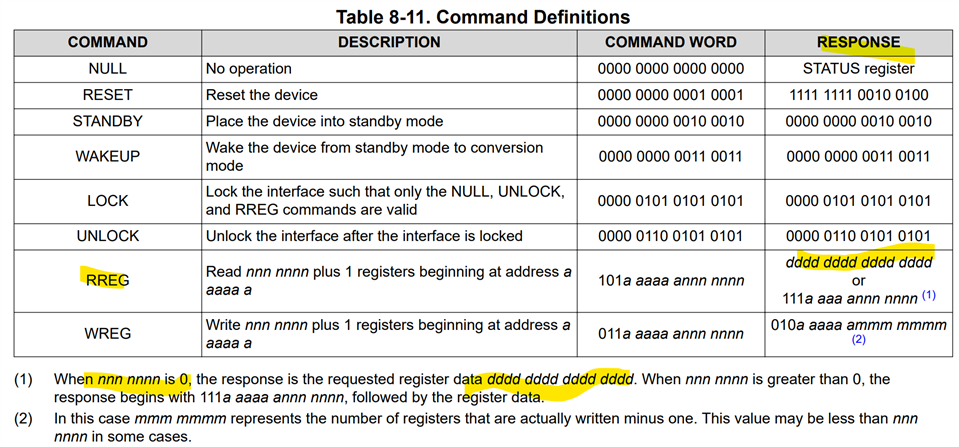

I read the EVM data sheet and the ADS one too. My goal is to be able to read and return readings from each ADS channel.

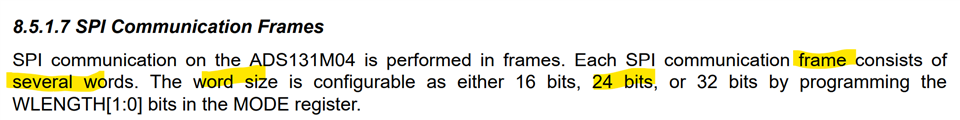

My PIC is setup for SPI1 Mode. 1MHz serial clock.

How can I verify that the ADC is getting the written data, if the DOUT is not outputting right?

Additional info, when I received the EVM, I used the PHI with GUI. I was able to capture and read/write registers. On the scope, the signals for DIN/DOUT were very noisy pulses.