Hi,

We have a custom board with ADC12DJ3200 ADC and Kintex UltraScale FPGA from Xilinx. We are using JMODE 0.

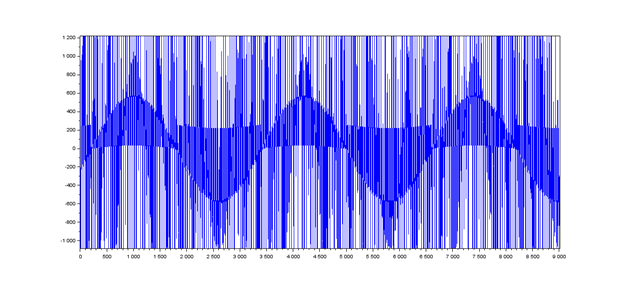

I am using the KCU105 reference design for JMODE 0, but the FFT is not fine.

So I tested short transport test pattern to check if the transport layer arrangement is correct, but even that didn't come fine.

As I am using the reference design, I don't expect the transport layer arrangement to be wrong. But I have no clue about what I am missing.

The sampling frequency is 1600MHz, K=4, Line rate is 6.4Gbps.

I have attached the screenshot of the Slice outputs of the reference design (probe0 to probe19 corresponds to slice_21 to slice_40 respectively and probe20 is the 240 bit transport layer output).

Looking forward to your support.

Thanks.