Hi Team,

My customer have issue with the device, please see details below for their concern.

I'm having an issue with the TI AFE 5832-LP with the Internal Non uniform setup for the board.

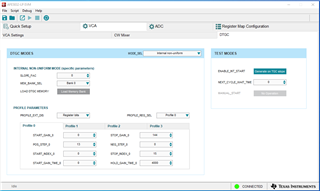

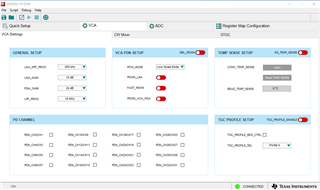

This is the DTGC parameters i have set

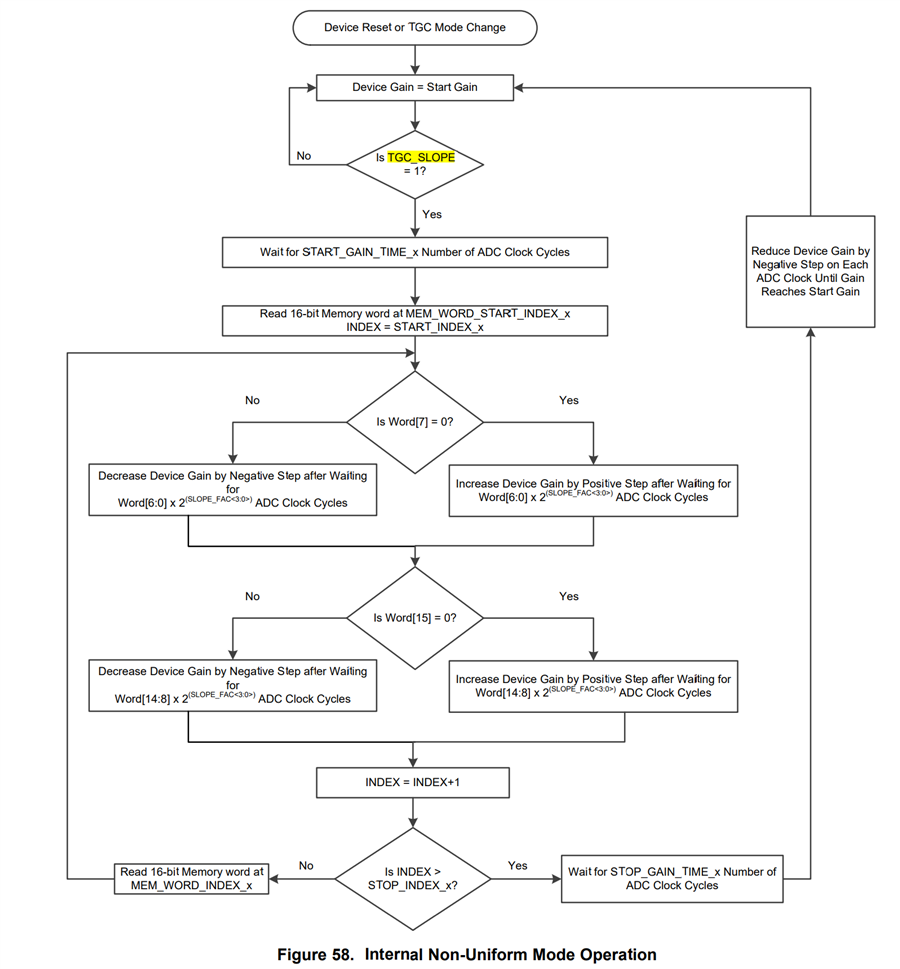

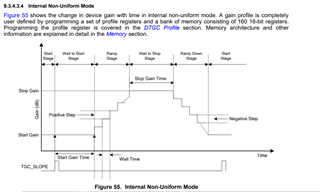

I will explain according to the user manual the signal I have used

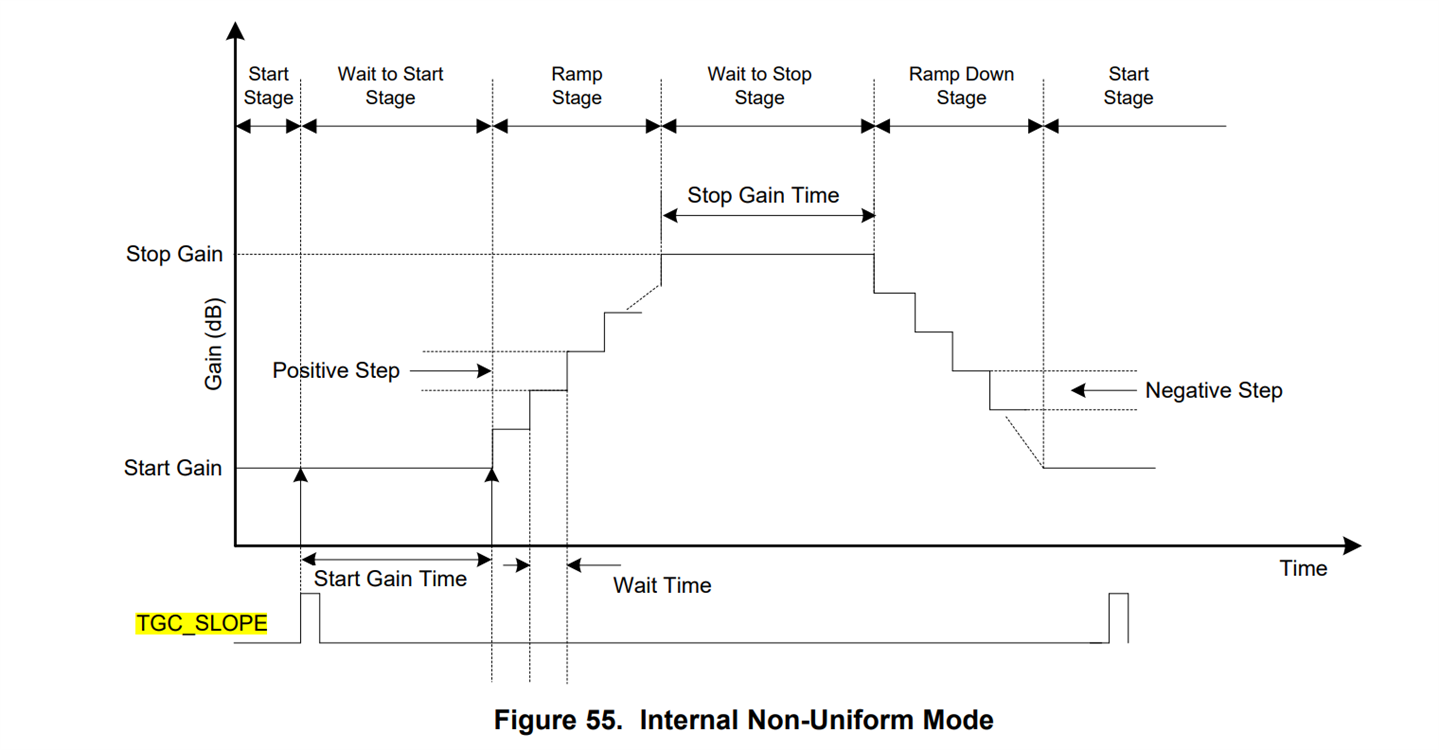

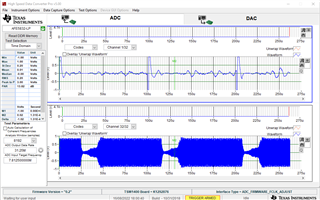

This is the mode i have used in which the TGC_SLOPE signal that was used in TP37 was my signal as seen in the next picture at ch #1

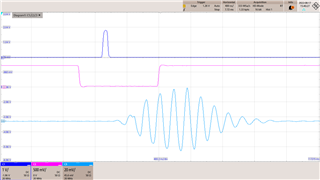

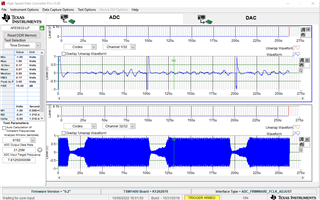

As you can see in channel 1/32 the TGC_SLOPE is accruing every 100uSec slope and the gain as in channel 32/32 is not in SYNC with that signal You can see that also next figure:

channel 32/32 is not starting at the same location as the pulse in channel 1/32 at times: 0 uSec and 100uSec 200uSec and so on. I would like that the gain will be very low at the points where in CH 1/32 the signal is high (above one volt as you c=vcan see in ch1/32) and if these channels will be in SYNC , then that high voltage will have low gain as you can see in ch32 where the gain have low value

Thank you.

Regards,

May