Other Parts Discussed in Thread: ADS54J60EVM, ADS54J60, ADS54J69, LMK04828, TSW14J57EVM

Hello TI experts,

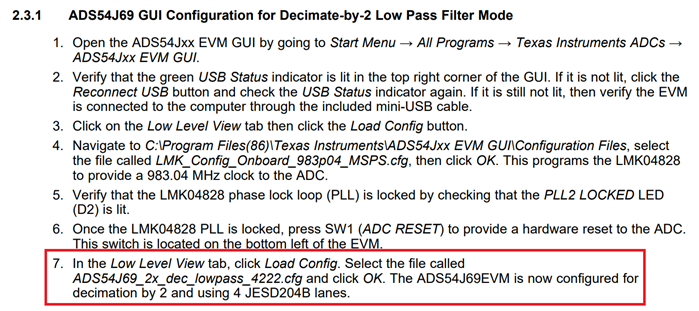

My customer tests ADS54J69EVM now, and here is one problem.

They tried to evaluate 2.3.1.7 in the User's Guide, but they could not find “ADS654J69_2X_dec_lowpass_4222.cfg” in any folder.

Could you check where this configuration file is? or please attach this file with your post.

Best regards,

Chase