Hi team

My customer has a questions about the calibration operation and could you help give the correct calibration process?

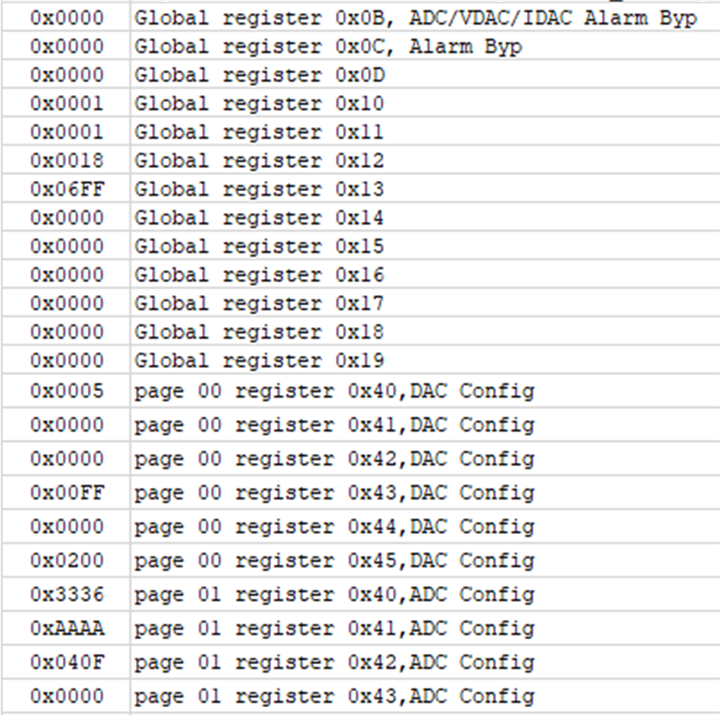

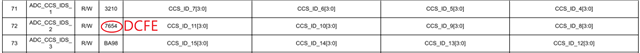

Register configuration:

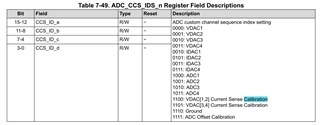

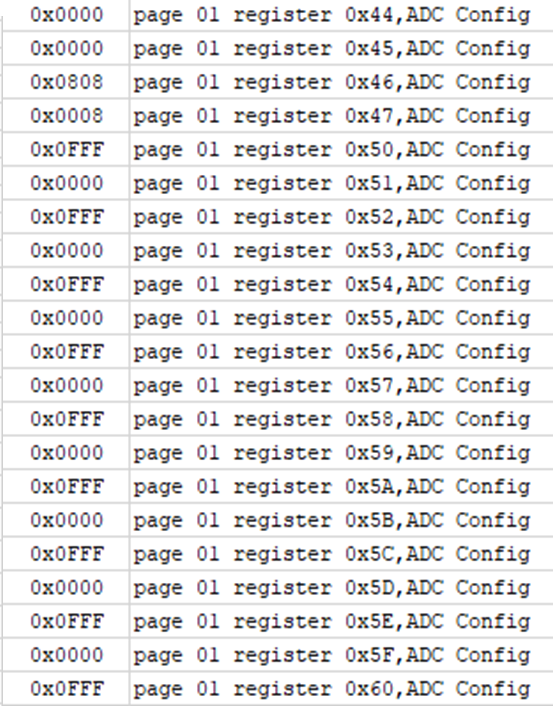

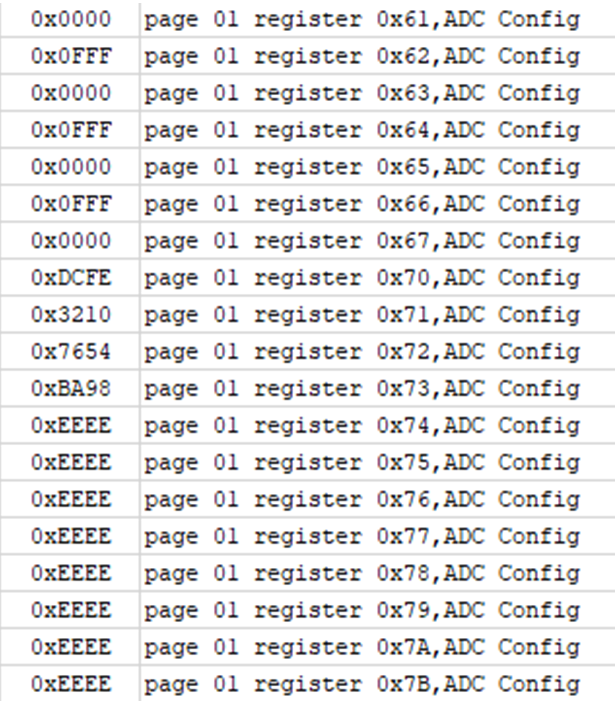

ADC_CCS_IDS_0(0x70)= 0xDCFE,

ADC_CCS_IDS_1(0x71)= 0x3210,

ADC_CCS_IDS_2(0x73)= 0x7654,

ADC_CCS_IDS_3(0x73)= 0xBA98。

ADC_CCS_CFG(0x42)= 0x010F。

ADC_GEN_CFG(0x40) - CMODE(bit2)= 1,Auto-mode。

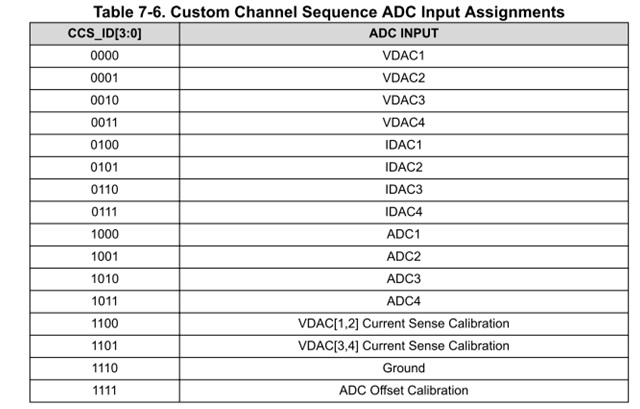

The customer wants the best accuracy performance but they are not sure if the calibration operation is needed for every conversion, D/S stats “To optimize the ADC performance, run a single conversion of the calibration channels at start-up”, could you help elaborate on it and give the correct calibration process step by step?

BTW, does AMC60804 support the calibration on the IDAC voltage sense calibration? D/S only shows the VDAC current sense calibration.