Hi

I have designed my own board with 4 ADS1298 chips. I can read write to registers. I can read out 32 channels. I have attached a signal generator to all channels. 29 out of 32 channels work fine. 3 channels provide some rubbish.

Alle channels and chips are configured the same way.

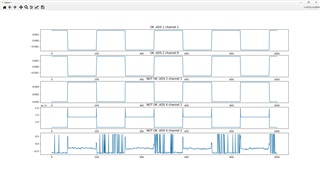

In the plot bleow you see:

Channel 1 Chip 1 And channel 8 chip 2 both looking fine. Allt the other channels look fine. Besides ADS 3 channel 1 , ADS 4 channel 1 and ADS 4 channel 2.

In fact for the plot I used the internal test signal. It is the same if I use a external signal generator!.

And I have the same behaviour on 3 different PCBs ;-(

Any Idea why those 3 channels behave this way?