Other Parts Discussed in Thread: RM48L952

Hello,

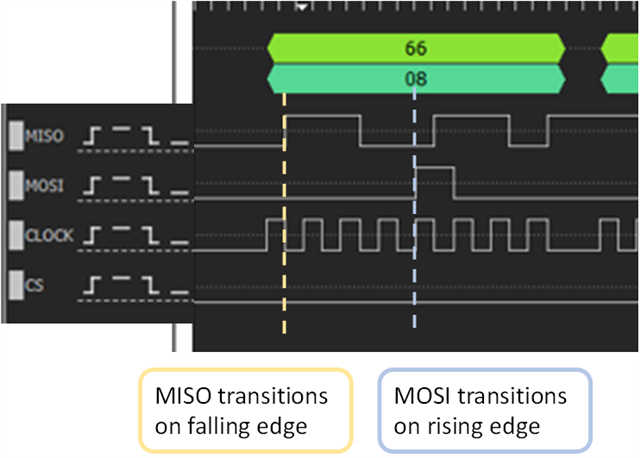

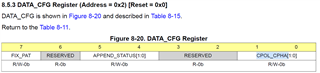

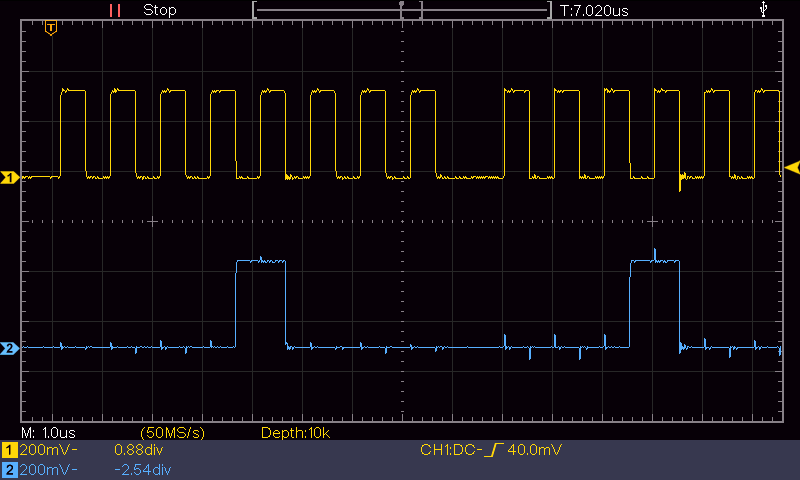

I have a custom board which embeds an external ADC with the part number described above. I want to read data from port 4 but all the time the read data belongs to port 1. Please find attached the SPI trace I use to read port 4 data.

Best Regards,

Cosmin Briceag