Other Parts Discussed in Thread: THS4521, ADS1278

Hi,

I am programming and reading from THS1206 ADC using Verilog. The final use of this ADC would be for piezo sensor. Currently, on the board all the defaults are considered as per the datasheet. There are few things those are not mentioned as listed below:

1. Can I tie the pins CS0 and CS1 permanently to GND and VDD respectively? If so, what are the potentials to be used (nominal 0V and 2.5V I feel)?

2. To read the data for a single differential channel (AINP, AINM) (others not used) with TL = 1, CONV_CLK = 6MHz, DATA_AV = active low pulse, VREF = internal, continuous conversation mode, sensor not connected yet:

What should be the time interval between RDbar and DATA_AV active (since datasheet says to read after DATA_AV active but before falling edge of CONV_CLK)?

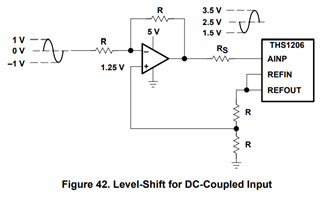

3. What should be the minimum input range for the above specs (both the inputs are clamped using DC Clamping circuit present on page no. 36)? Is it possible to read when I short/open the input terminals?

4. If I do not clamp, is it possible to realize the noise behavior/ENOB/Noise free bits with shorted inputs?

5. While configuring the CRs should there be any time gap required? Can I send config word in consecutive clocks?

Thanks