Hi

We want to find out the maximum possible input rise/fall time of ADS7049QDCURQ1. Therefore, we find out a TI application note. We understood that if we have the input transition rate and VIH(min) and VIL(max), then we can find out the rise/fall time using the following equation:

Here, VIH(min)=2V and VIL(max)=0.8V.

Is this approach correct?

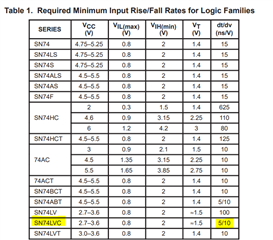

Also, in the TI application note, does the transition rate, (dt/dv) of SN74LVC mean 0.5ns/V. Please confirm.

Regards

Sreelekshmi.