Hi team:

My customer use AMC7836 in their DAS remote units by using two pcs AMC7836 for amplifier gate voltage read and write control, with a XILINX FPGA as the host and three slave devices hanging under the SPI bus: two AMC7836 (AD/DA chips, AMC7836_1, AMC7836_2) and one AD9543 (clock chip). The SPI bus is terminated with 22Ω resistors.

Here is the fault phenomenon:

1. At room temperature, all chips can run stably. At low temperature -40℃, it was found that the output gate voltage value of AMC7836_1 oscillated back and forth in an irregular manner, and the corresponding registers (1e, 1f) of AMC7836_1 also oscillated repeatedly, while AMC7836_2 and AD9543 were normal.

2. After changing the SPI resistor value to 33Ω, the abnormal phenomenon of AMC7836_1 at low temperature was greatly reduced, but after repeated experiments, there were several exceptions.

3. After changing the SPI resistor to 0Ω, AMC7836_1 will be abnormal at room temperature. The attachment includes the test waveform of 7836-1 when an exception occurs.

Please help to analyze the cause of the 7836 exception, thank you!

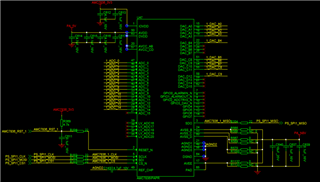

Circuit diagram:

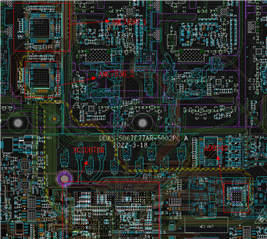

PCB layout: