Other Parts Discussed in Thread: ADS1298,

I have designed a functioning prototype using the ADS1299 ADC. I am digging into the bias amplifier and input filters at this time and need to understand

a little more than what the datasheet provides. I will reference the ADS1299 datasheet SBAS499C revised January 2017, the evaluation kit user manual

for the ADS1299 (EVK), SLAU443B revised January 2016 and the application note SBAA188 "Improving Common-Mode Rejection Using the Right-Leg Drive Amplifier" July 2011 I came across a few typos in the datasheet and app notes. If I'm incorrect, please let me know. In the datasheet section 10.2.2 talks about the gain set by Rbias although figure 73 shows this as Rf. I take it these are the same. In SBAA188 Figure 7 input filter capacitors show 47nF although the ADS1298 PDK schematic show 47pF. In ADS1299 datasheet, Figure 73 shows the input summing resistors as 220K. Equation 11 and nearby text refer to these as 330K. The ADS1299 can be set up to measure the bias amp input resistors itself. Set channel 2 ADC for shorted lead test with gain of 1 and enable BIAS2N and BIAS2P.

Connect channel 3 to BIASIN in bias measurement mode and enable the bias amplifier. Note that channel 1 BIAS1N and BIAS1P cannot be enabled with the EVK application,

likely a software bug. Read ch3 for Vout of the Bias Amplifier. The shorted lead test will bias the output to -0.25V on BIAS2N and BIAS2P, that is, it connects (VREFP + VREFN)/2 through a resistor to the programmable

gain amplifier (PGA) inputs. The inverting summing amplifier is Vout = -((Rf/Rin1) * V1 + (Rf/Rin2) * V2 ... ). The EVK has 392K ohm for Rbias (Rf) and the

bias output measured about 0.9V. Since all input resistors are the same, Vout = -(Rf/Rin) * (V1 + V2) and

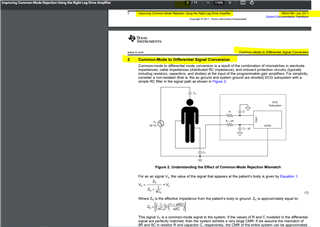

solving for Rin = -(Rf * (V1 + V2))/Vout = (392Kohm * (-0.25V + -0.25V)/0.9V = 218K ohms. This is within 1% of 220K. So I take it equation 11 has the wrong value input resistor. Onto the questions I have. It is my understanding from datasheet 9.3.2.4.5, that the bias amplifier (or driven right leg - DRL), takes the common mode noise (CMN) from the PGAs,

amplifies it, inverts it and then feeds it back into the human body to further reduce the CMN. This is predominantly AC line frequency (50Hz/60Hz). It is a

closed loop system with the bias amp, human body/electrode model, input filters and PGA in the loop. The datasheet and SBAA188 app note only says the feedback

capacitor sets the bias amps bandwidth but there is no further explanation as to what the bandwidth should be set. Using fc = 1/(2*pi*R*C) it is set it to 106Hz

in the datasheet. The EVK has a gain resistor of 392K and Cf of 0.01uF (R8/C20) for a minimum DC gain of 1.78 and -3db cutoff at 40.6Hz.

For the bias amp to work properly shouldn't this filter pass the line AC frequency without attenuation and phase shift? If so, why is the EVK bandwidth lower

than the dominant CMN? I would appreciate a more thorough explanation of what the target bandwidth is for bias amplifier's low pass filter and reasoning

behind selecting that bandwidth. The next issue is determining the cutoff frequency of the input filters (Rfilt/Cfilt). From section 10.2.2

"The cutoff frequency for the filter can be placed well past the data rate of the ADC because of the delta-sigma ADC filter-then-decimate topology. Take care to

prevent aliasing around the first repetition of the digital decimation filter response at fMOD."

The goal is clearer here, you should have sufficient stop band at fMOD and above to band limit the input sample rate and provide sufficient passband

for the bandwidth of the output sample rate. You can derive from Table 1,2,3 in the datasheet that the bandwidth is approximately the output sample rate / 3.817.

The datasheet only shows 4.99K ohms and 4.7nF for input RC filter in Figure 74 example. This is the same first order input filter used on the EVK with -3db cutoff at

6.79KHz. It would have -47db attenuation at fMOD and the cutoff is well above the bandwidth for 16Ksps setting. If I was only going to use 250sps, could I

decrease the cutoff of the filter to improve the stop band attenuation at fMOD. Maybe or maybe not. In SBAA188 and in a blog "Three guidelines for designing anti-aliasing filters", there is an equation

CMR = 20 log ((Rtol + Ctol)/100) + 20 log(f/fc)

where fc is the cutoff of the filter and f is the CMN. SBAA188 goes on to say it may be better to have a larger bandwidth for the filter to improve CMR.

While I have found several instances in articles for that formula, I have yet found a derivation and theory behind it. CMR (CMRR) is the ratio of differential and common mode gain (or losses) in db. In the formula above, neither the tolerances nor frequency seem directly

related to the gain/loss of a filter stage and while 20 log(f/fc) could approximate the slope of the stop band for f > fc, it is not a model for

low pass filter gain. So if there is an in depth proof of this formula, could I get a reference to it? If not, could someone explain the theory behind it?

Thanks