Part Number: ADS1291

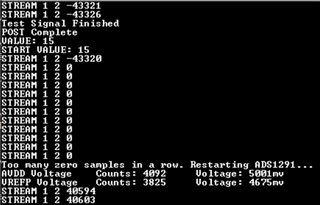

I'm currently working with an ADS1291, and verifying that it can generate test signals, as well as read signals passed in. Currently, I'm occasionally getting back 0 responses when reading the ID register, when reading back the configuration settings, and when reading data after a data ready signal is received.

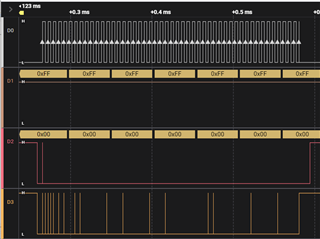

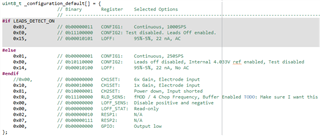

It's more often than not that I receive these issues, but most of the time, I'm able to successfully write and read back the test signal configuration. Even if I read back an ID value of 0 afterwards however, it's still able to generate the test signal. Once the test signal has been fully processed, I try to write the normal operating configuration, and it usually fails by sending back 0 somewhere in the process. I've included images of my configurations below.

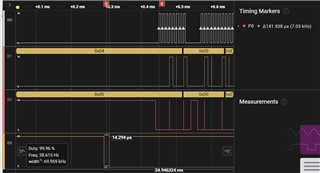

My configuration changing process is as follows:

1. Wait 4096 TMOD cycles after startup (31,998uS)

2. Set RESET high and wait 1 second

3. Set RESET low and wait 1 TMOD cycle (8uS)

4. Set RESET high again and wait 18TCLK cycles (36uS)

5. Send SDATAC command

6. Write 0xA0 to CONFIG2 for PDB_REFBUF

7. Wait until VREFP reaches at least 2.2V

9. Write 11 bytes of config to CONFIG1 register

10. Wait 18 TCLK cycles (36uS)

11. Read back config register and verify it matches the config passed in

12. Read ID register and verify it matches expected value of 0x52s

13. Send START command

14. Send RDATAC command

It seems as though most of the time it sets the configuration for the test signal properly, but it's not surefire. It's seemingly random where it fails when changing to _configuration_default, but most of the time either reads a 0 back when verifying the configuration, a 0 back when verifying the ID, or a stream of 0s triggered by the data ready pin.

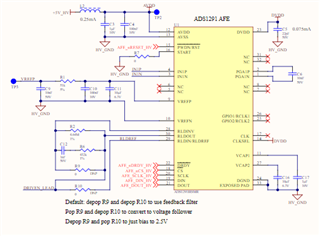

Our SPI is currently set to CPOL0 CPHA1 and 500kHz transmission rate, and this is the hardware configuration we're currently using in case that helps.