Other Parts Discussed in Thread: CDCE62005

Hi Team,

My client has a problem:

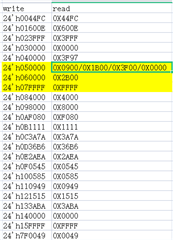

DAC1 and DAC2 analogs' output signals are not synchronous (single-chip with synchronous two-channel output). At present, the DATACLK and DATA signals input by the FPGA to DA1 and DA2 are all in a synchronous alignment state measured on the pins of the DAC chip. The SYNC1 and SYNC2 signals are aligned (pulse rising edge), and the ALIGN1 and ALIGN2 signals are aligned (pulse rising edge) too. There is a phase difference in the analog output. The description in the datasheet about how to use the ALIGN signal is not very clear. If I want to realize the synchronous output of two DACs, is there any modification that I could make?

Specifically, the DAC adopts the default register state mode, NORMAL Dual Sync mode. After power-on, the DAC is reset and then starts working with the default mode.

I read the document https://www.ti.com/lit/an/slaa584/slaa584.pdf, but I still don't know if I want to ensure that there is no difference in DAC analog output, what configuration should I make? Could you offer me any documents for references?

Could you provide technical support?

Kind regards,

Katherine