Hello,

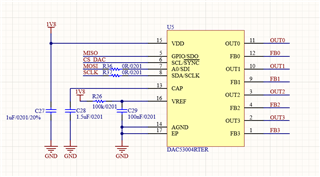

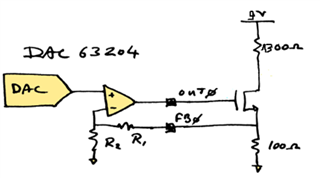

I am using the DAC53004 to control the current in a load with a force-sense configuration with a MOSFET:

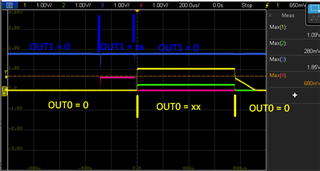

We are doing pulses of 50us/250us, with about 20ms rest in-between. During the resting, 0 is sent to registers DAC-X-DATA (19h, 1Ah, 1Bh, 1Ch).

The gain is 1.5 and the reference used is 1.21V.

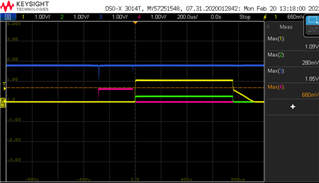

The problem is, sometimes in one of the channel OUT I can see 1.8V during the resting time, instead of 0V. It saturates for some reason.

This is what I am seeing. Blue is OUT1 and Pink is FB1. Yellow is OUT0 and Green is FB0.

The OUT0/FB0 is what I am expecting, and the OUT1/FB1 is what is going wrong.

Do you have an explanation for that?

Best Regards,

Aurélie