Other Parts Discussed in Thread: TSW14J50EVM

Hi Experts,

Seeking your assistance on this hardware issue with ADC32J25EVM and TSW14J50EVM data capture. Customer shared his reports below.

I have it all set up and working with the software and the fft being shown. However I am seeing a 10-15db noise on 1 of the channels and cannot understand how this might be the case? is this something you can help with?

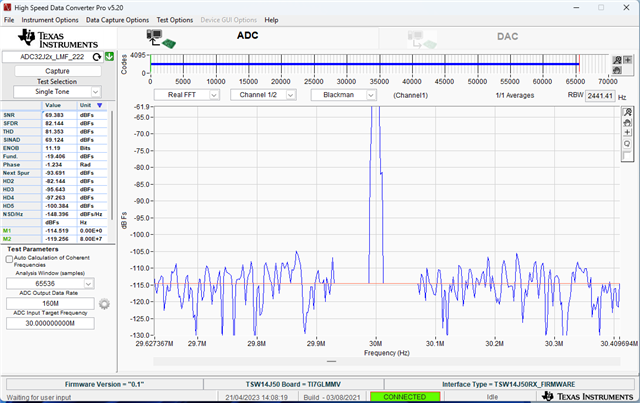

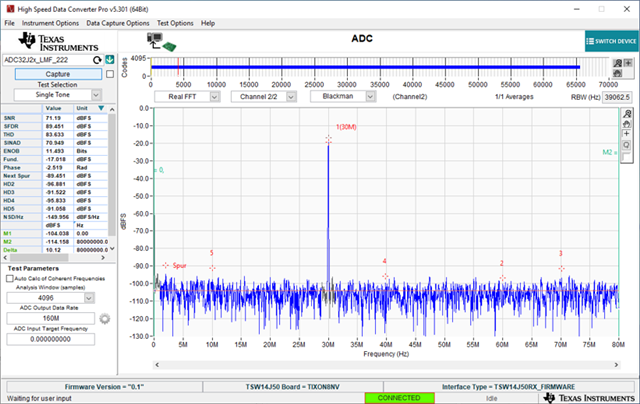

I have set up the 2 boards aas per the user guides. Channel 2 has a noise floor of approximately -110dB with channel 1 having a noise floor of -92dB. the fundamental frequency amplitude is consistent in both cases so it can only be noise within one of the channels. The board however looks identical so I and my colleagues cannot understand why this might be.

I have sent the 2 screenshots illustrating the difference (attached)

Regards,

Archie A.