The datasheet states in the section titled Power-On Reset on page 16 that "After power-up, the output from pin VOUT of the DAC8830 is 0 V."

In our hardware we have found this statement to not always hold true. After bootup our DAC8830 VDD pin has 5V, the reference reaches 5V, and when we start communicating with the DAC, we have the expected SPI based control of Vout. However, at power on and before communication, sometimes the DAC will power on with Vout = 0V and other times the DAC comes up with Vout = 5V or 2.5V or 3.4V. We are using 16 of these DACs in the system and each has its own stable output voltage that it will go to when we boot into this "wrong state". I have verified that our SPI CLK is quiet except for a single rising edge on power-up, do to a design choice that idles the clk high. I assume this means that I can't be loading in a non-zero value in to the DACs until my intended communication begins.

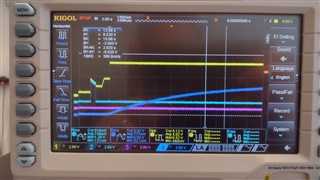

The only difference I can find between when the DAC starts with Vout = 0V and Vout equaling some other voltage, has to do with our voltage reference which has a very slow time constant of 10 seconds. When the reference is stable, 5V, and we reboot the system, then Vout = 0V on every DAC. Note that the reboot process does not give enough time to bleed off the voltage reference, so when the DAC powers after reboot the 5V reference is present. However, when the system is turned on for the first time after a long wait, 30s, then Vout rises in sync with Vref until Vout reaches the non-zero start-up value. Since Vref needs 10s to get to 70% of 5V, it is not present during the power on sequence in the cold start case.

So my question is this, how is the POR achieved and could the absence of Vref at power on somehow thwart the function of the POR? or is there some other reason the DAC might start with a non-zero Vout?

Any help is appreciated.