Part Number: ADS1014-Q1

Other Parts Discussed in Thread: ADS1014, , ADS1114-Q1, ADS1015

Hi Team,

Can you please help with the question below?

On the datasheet Page 10/44

1. Why the 1-MHz internal oscillator has to be divided by the factor of 4? Is it because of the internal modulator was designed to run at a frequency of 250kHz. ?

2. If the modular frequency is 250KHz, according to Nyquist theorem which says 'a periodic signal must be sampled at more than twice the highest frequency component of the signal'. So in this case, the maximum frequency that could be sampled is Fmod/2 (250kHz/2) = 125KHz for ADS1014?

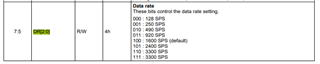

3. It is to be understood that there are several rates for data conversions such as 128 SPS, 250 SPS, 490 SPS, 920 SPS, 1600 SPS, 2400 SPS, or 3300 SPS. This can be configured by the given register in DR[2:0]. Configuring this will also change the Fmod rate at the input sampling.

4. According to Table 7.6 on page 22, Bit 7:5 Field DR[2:0] description says the binary bits for a maximum of 860 SPS only. How do we can set it for 3300 SPS and other SPS mentioned in Question 3?

Thank you.

Regards,

Marvin