Other Parts Discussed in Thread: DAC8771, , DAC8775

Dear Team,

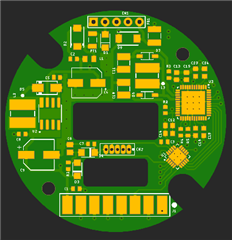

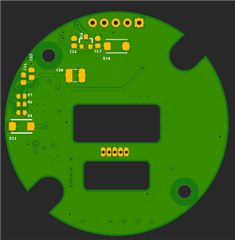

I'm designing a 4-20mA, three wire, current loop interface.

In order to reduce the power dissipation of the output stage I'm using the Buck-Boost integrated stage.

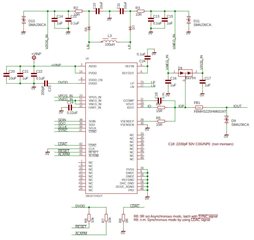

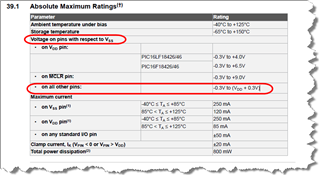

Following the notes reported inside the DAC8771 (SLASEE2 - Feb 2018) on page 66 I think that the right config is the one show into the Figure 130 where the VNEG_IN is tied to 0V, I'm right?

If this is the proper connection I think also that I've to disable the negative leg of the Buck-Boost because not used due to unipolar output type (4-20mA) so into the register 0x07 I've to use PNSEL[1.=]=01, right?

Regarding the protection TVS on the VPOS_IN, from the DAC8771EVM schematic there is a resistor named R2 (10R 0603) the purpose of this is to limit the current inside the output capacitor C1 to limit the voltage drop in the event of a voltage spike from the output?

Thanks and best regards.

F.