Other Parts Discussed in Thread: LMK04828, , ADC32J24

Hello,

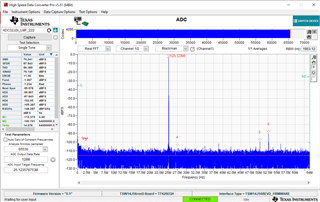

Now we have the board, and the board has been verified including the clock generation with LMK04828 and FPGA

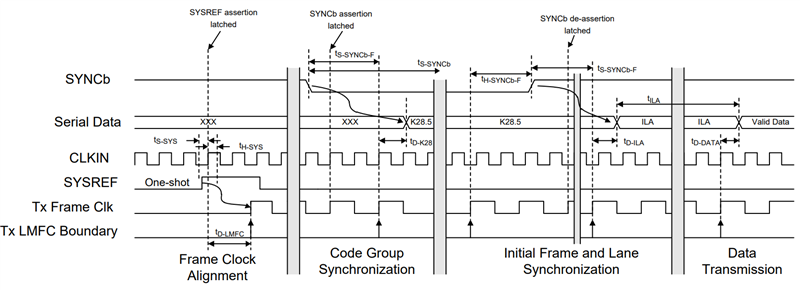

We are now trying to get the JESD204B working between ADC32J25 and FPGA.

We are leveraging a previously working FPGA design with JESD204B.

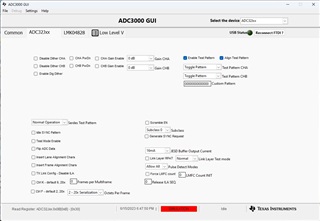

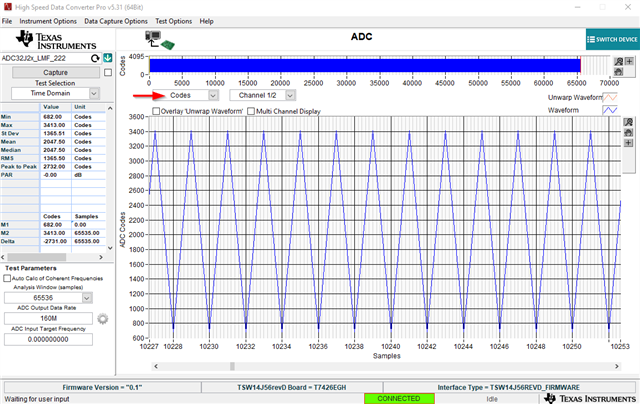

The 1st step is to see if we can receive a test pattern from ADC32J25.

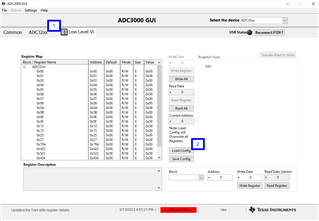

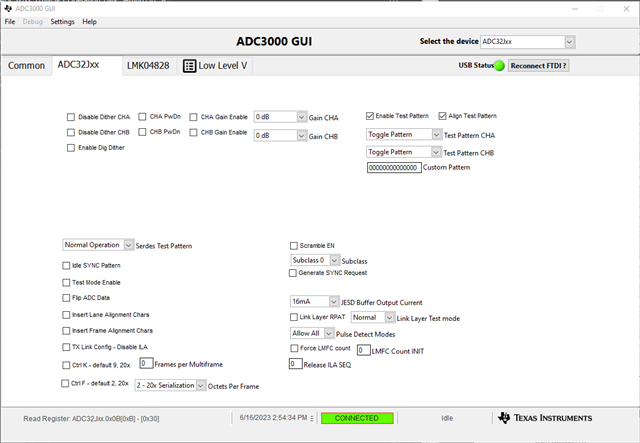

Attached is the ADC register configuration.

Would you be able to take a look at the configuration?

Regards,

Andrew

00400100 00400300 00400400 00400602 00400700 00400800 00400900 00400A03 00400B30 00400C00 00400D00 00400E00 00400F00 00401300 00401500 00402700 00402A56 00402B01 00402F00 00403001 00403114 00403420 00403A00 00403B40 00403C00 00442200 00443400 00452200 00453400