DDC232CKについて質問があります。

仕様書"32チャネル、電流入力A/Dコンバータ"のP18のTable11によると、

tncdr1はCLKの周波数で決まるように読み取れます。

仮に20MHzで設定した場合,67.8usになるのでしょうか?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

DDC232CKについて質問があります。

仕様書"32チャネル、電流入力A/Dコンバータ"のP18のTable11によると、

tncdr1はCLKの周波数で決まるように読み取れます。

仮に20MHzで設定した場合,67.8usになるのでしょうか?

Hi Kodashima-San,

Excuse me. I learned Japanese, but not yet good enough to understand and reply in Japanese.

And, official language for E2E is English.

So, would you please use English so people can read&understand as well?

I guess you are asking questions related to clock cycle or frequency related to ADC?

Thanks

Hi Chien Chun Yang-san.

I will write my question in English.

I have a question about the DDC232CK.

According to Table 11 on page 18 of the specification "32 channels, current input A/D converter", tncdr1 can be read as determined by the frequency of CLK.

Is it correct to understand that tncdr1 will be 67.8us if the CLK frequency is set to 20MHz?

Hi,

Thanks for writing in English.

Unfortunately, I still don't understand your question clearly.

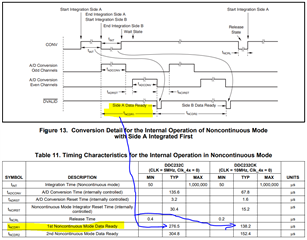

If looking at datasheet page 18, figure 13 and Table 11.

tncdr1 means the time duration needed between the falling edge of CONV to the falling edge of /DVALID. And this tncdr1 time could be different length depending on the device(DDC232 or DDC232CK) AND the CLK(5MHz or 10MHz)-

Not sure what you mean by 67.8 us or 20MHz?

Thanks

Hi Chien Chun Yang-san

Thank you for your reply. Sorry for not being able to ask the question well.

The value was slightly wrong.

As for the question,

Data sheet page 18, Figure 13 and Table 11 are the specifications when CLK_4x=0.

I would like to know the specifications in Table 11 when CLK_4x=1.

When I set CLK_4x=1, I read that the DDC232C behaves as follows.

• When CLK_4x=1, the frequency of CLK is quadrupled, so CLK becomes 20MHz.

• When CLK is quadrupled, tncdr1 becomes 1/4. So 276.5/4 = 69.1us.

Please let me know if there is anything wrong with my interpretation.

Hi,

From page 3, for DDC232C,

if wanting to set CLK_4x=1, the System Clock (CLK) has to be between 4 to 20 MHz.

Then, due to CLK_4x=1, thus Clock Divider = 4, so the INTERNAL CLOCK FREQUENCY becomes 4MHz/4 = 1MHz to 20MHz/4=5MHz, which is used to generate the Data Valid(/DVALID) signal discussed in page 14. And, this implies signals that may depend on the INTERNAL CLOCK frequency are now 4 times slower.

Page 16 says -

Figure 11 through Figure 16., Table 9 gives generalized timing specifications in units of CLK periods for Clk_4x = 0.

If Clk_4x = 1, these values increase by a factor of 4, i.e. longer time, 4 times slower, as I mentioned in the above paragraph.

so, take Table 11's DDC232C's tncdr1 as example, if using CLK=5MHz and set CLK_4x= 1, then , tNCDR1's typical will become 276.5 * 4 = 1106 us, i.e. slower and longer.

Thanks