Other Parts Discussed in Thread: DDC264

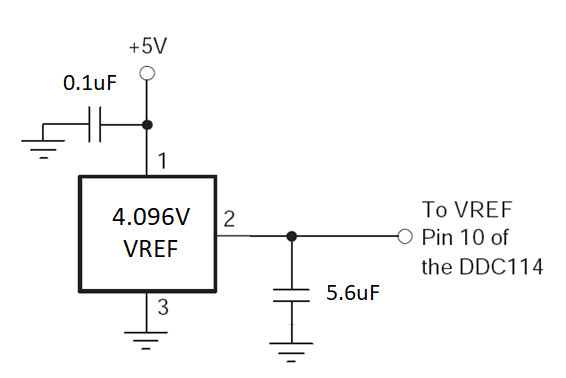

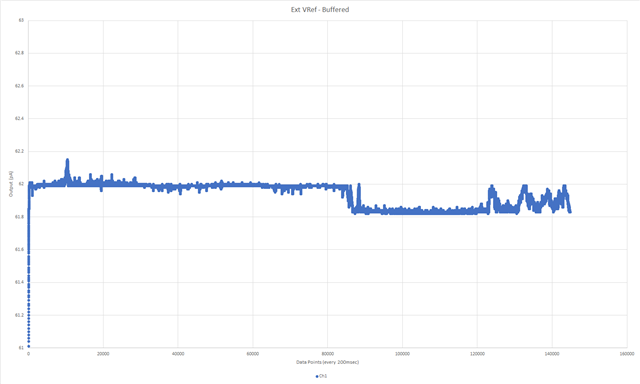

I am currently investigating a problem with DDC114, where the ADC value is gradually changing with time, as shown below. Moreover, the extent of this drift differs among different boards. Is this a known issue associated with DDC114? If so, are there any potential workarounds available to address this issue?

Additionally, I would appreciate your kind recommendation for a pin-compatible replacement IC that offers superior performance compared to DDC114IRTCT.