Other Parts Discussed in Thread: LMX2594, LMK04828

Hi,

I have questions about the dual channel work mode and onboard clock.

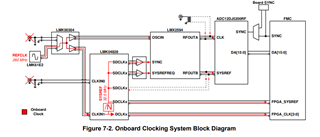

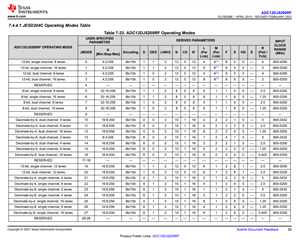

1. The max sample frequency of onboard clock is 10.4GHz/single channel & 5.2GHz/dual channel? I have looked through the user guide and datasheet, it seems LMX2594 is powerful enough to provide 5.2GHz sample clock, but there is not an exact answer.

2. If the dual channel work mode is selected, what should I do? If there exists some user guide to which i can refer(We have TSW14J57). And the dual channel are synchronized?

Thanks