Other Parts Discussed in Thread: ADC12DJ3200

Good afternoon,

We had a design with the Xilinx JESD IP using the ADC12DJ3200 that was working correctly.

We did not test it for a week or so and the next time we turned it on the GTH_RXBUFSTATUS signal was varying wildly.

Sometimes it was showing elastic buffer overflow, elastic buffer underflow, etc, etc.

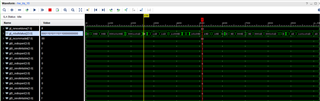

Like this:

What could be the cause of these issues?

What information can I provide that may help debug this issue?