Other Parts Discussed in Thread: DAC161S997

We've been testing a product that uses this ADC to convert a mV pressure transducer signal to 4-20mA output current with the DAC161S997 and a microcontroller.

When we apply a IEC 61000-4-6 test with 3V p-p 80% AM common-mode RF interference (0.15-80 MHz) with a EM clamp injection to the loop wiring (unshielded twisted pair), I get a quite significant DC offset shift in the ADC output at certain frequencies.

The EM clamp is on the portion of loop wiring with one conductor going to the positive terminal of the 24VDC power supply and the other conductor going to a Fluke loop calibrator and through it, back to the negative terminal of the power supply.

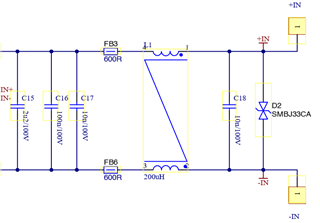

The loop wiring before the DAC161 and the 3.3V linear regulator has the following filters

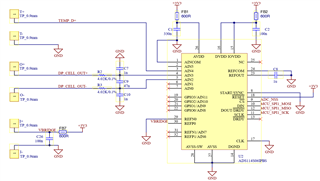

and we are using the ADC in the following way

We've tried with several variations of removing the CM choke, changing the ADC bridge input filters, and so on, but nothing seems to help for this particular product.

I would greatly appreciate any help anyone can offer as I'm mostly out of ideas at this point.