Other Parts Discussed in Thread: LMX2594, SN74LVC8T245, TXV0108-Q1, SN74LV4T125, SN74LV1T126

Hi,

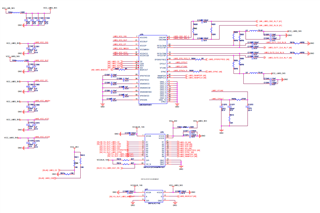

In ADC12DJ5200 EVAL board LMX2594 device inputs like CS, SCLK, SDI signals coming from FPGA are level translated to 3V3 from 1.9V using SN74AVC4T774RSVR device and outputs from level tranlator are connected to FET Multiplexer. I have query on the 3V3 level tranlation.

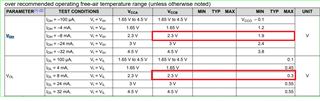

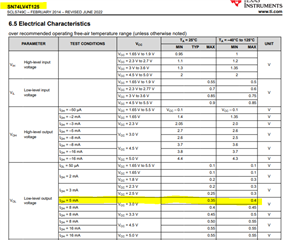

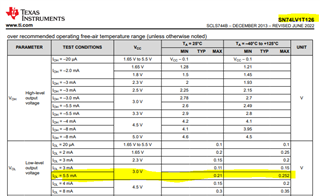

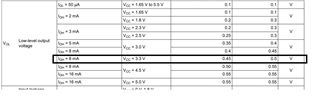

For Level translator IC SN74AVC4T774RSVR Output voltage levels at 3.3V are VOH level is 2.3V and VOL level is 0.7Max, whereas LMX2594 device input logic levels are VIH level is 1.4V and VIL level is 0.4 Max.

How both devices are compatible with each other, level translator VOL is higher than the VIL level of LMX2594 Device.

In my case, my FPGA will support only 1.8V level whereas LMX will support 1.8V to 3V3. If I want to connect CS, SCLK, SDI signals directly from FPGA then VOL(max) is higher than LMX VIL (max). I have to convert 1.8V levels to 3.3V, in this case almost all the level translators output logic level at 3.3V is VOH level is 2.3V and VOL level is 0.7Max. which will create issue for 3.3V level

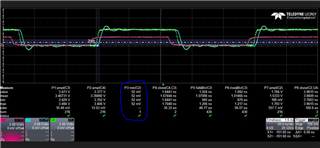

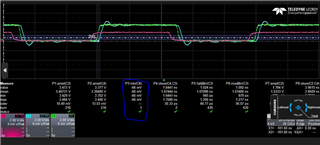

So, Instead of converting it to 3.3V Iam converting it to 2.2V so that Output level of level translator will match to the LMX2594 device inputs.

Please find the below given image for the same.

I want to know that in eval board how that logic working?

Do we need to really do the level translation for this issue, or from FPGA directly can we connect all LMX2594 devices?

Please clarify.