Hi,

I have customer who use this chip and have some design issues.

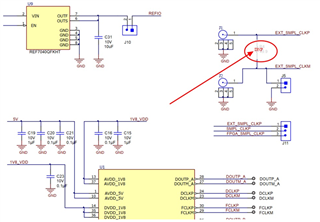

1. Whether this chip can be input with differential clock? Differential is available on the EVM, but it is not written in the datasheet.

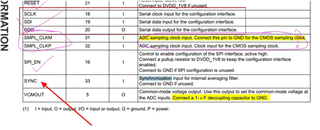

...

2. What does DNP mean on EVM?

3. How does SYNC work? The manual gives less information.

Many thanks~