Hi expert,

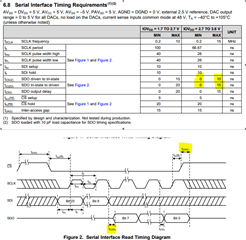

Customer used AMC7834 and have some questions about SPI timing spec e.g. ODZ and OZD although so far no any communication issues.

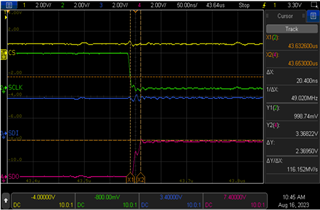

What customer measured tODZ is -452ns(spec: 0-10ns) and tOZD is 20.4ns(spec:0-15ns) which are all over the DS timing spec.

Please help clarify our measurement method or any misunderstanding.

tODZ:

Q1: referred to fig.2 in DS, is it correct that customer measured tODC from 50% rising edge of /CS to the last bit of SDO? If so, tODZ is -452ns which is negative and over the 10ns spec.

tOZD:

Q2: referred to fig.2 in DS, is it correct that customer measured tOZD from 50% level of SCLK before the first SDO bit? If so, tOZD is 20.4ns which is over 15ns spec.

Regards,

Allan