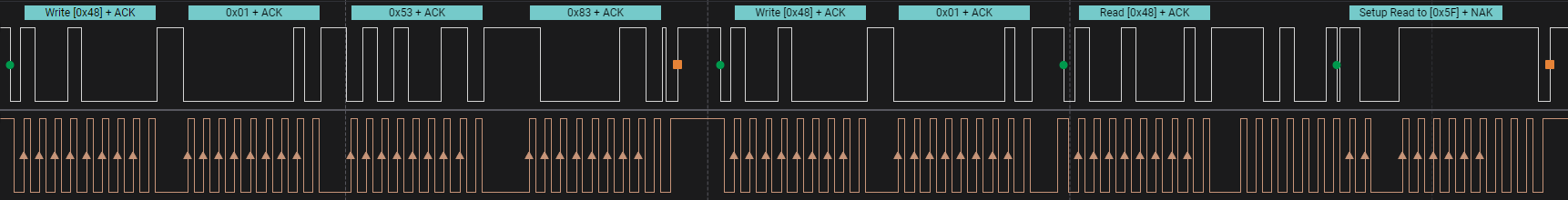

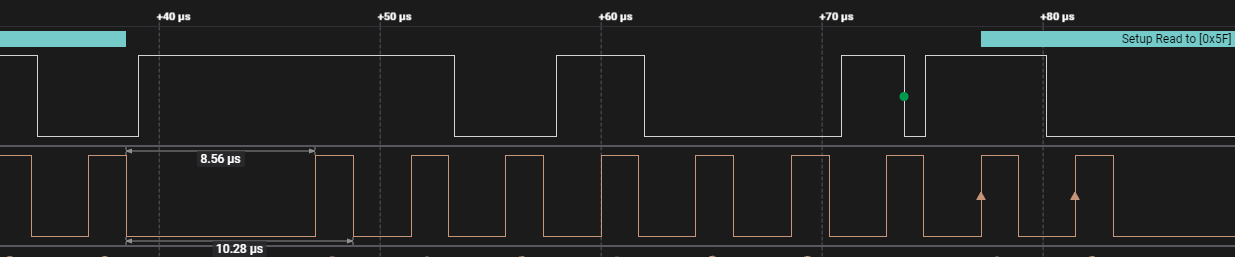

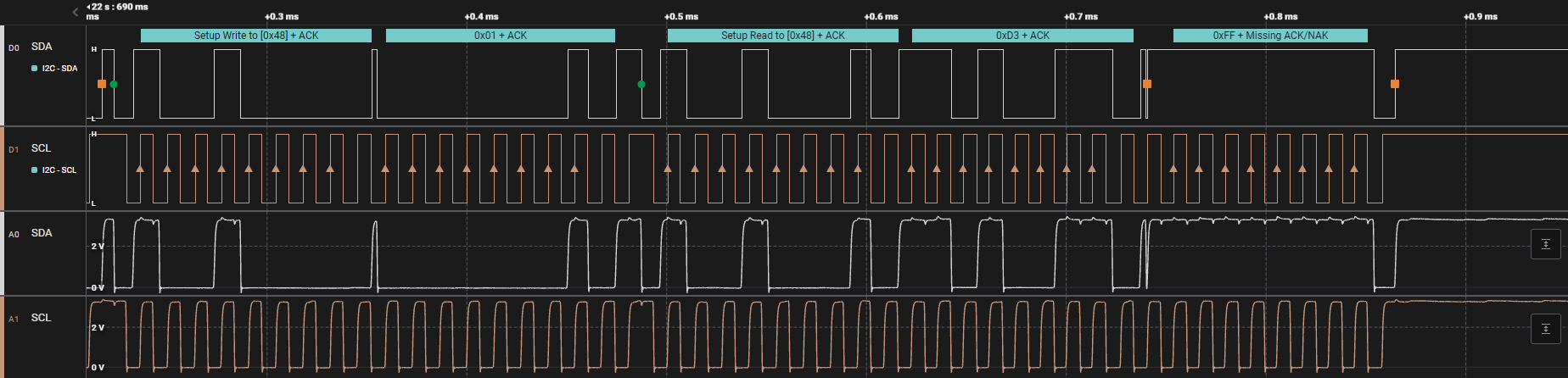

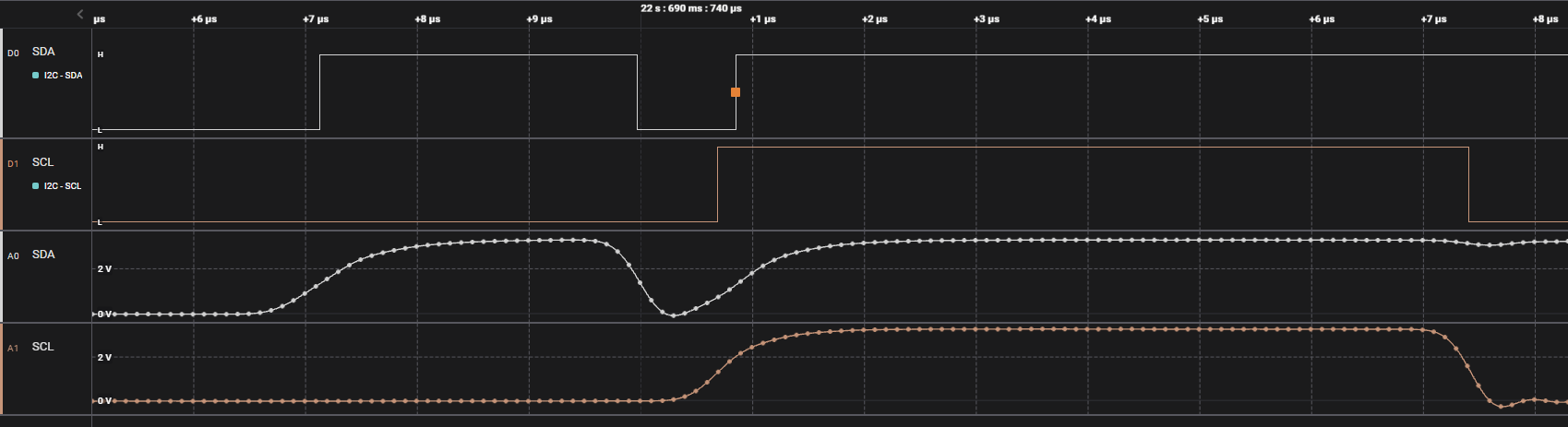

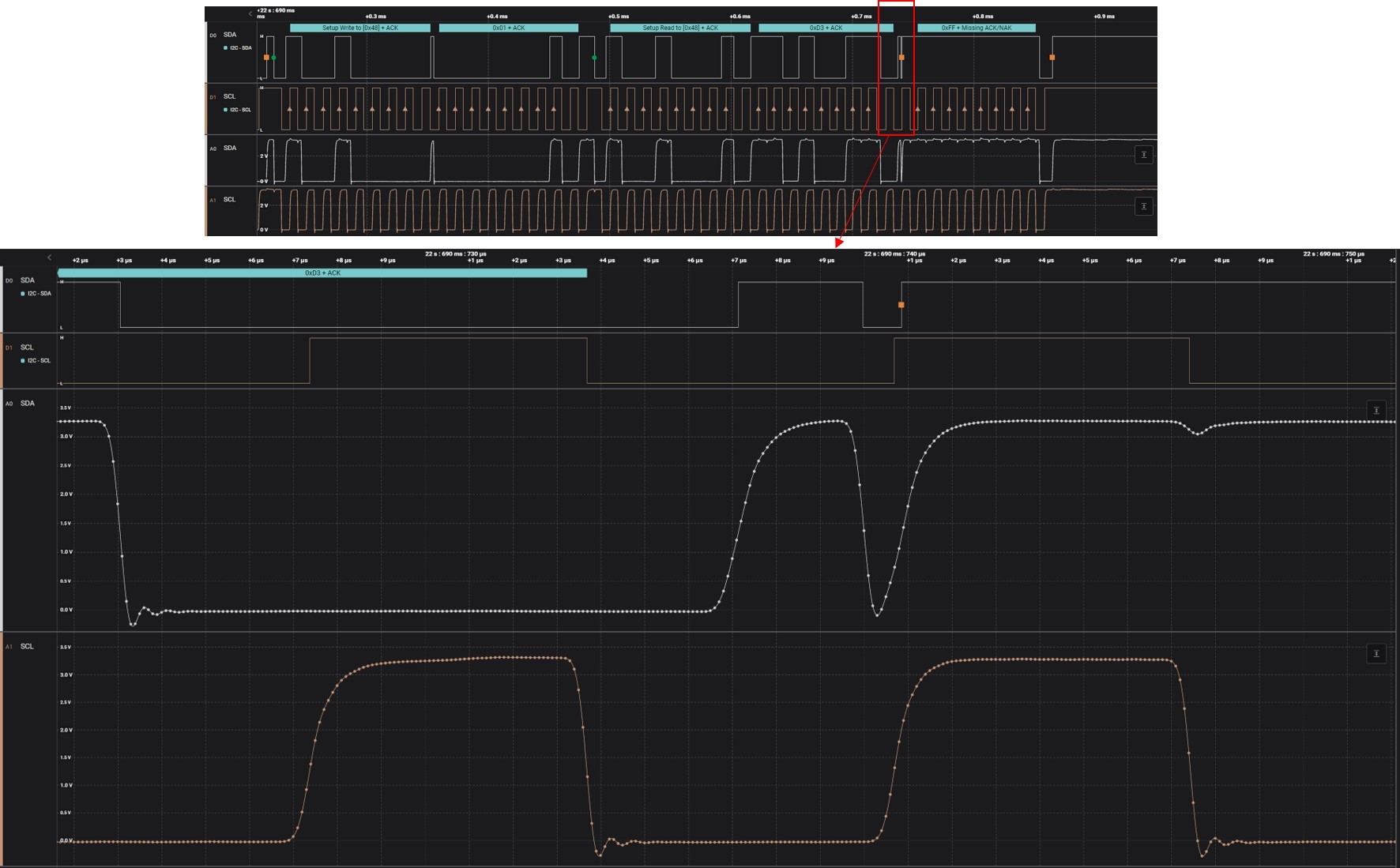

The following images depict a scenario in which, after writing 0x5383 to the Configuration Register (0x01) of TLA2024 (0x48), then immediately subsequent read of that register yielded a value of 0xD3FF. There appears to be an issue in the waveform after "Read [0x48] + ACK." The enlarged view of that portion of the waveform is shown in the second image. This phenomenon is observed especially at low temperatures (around -20°C) and occurs approximately once every few hundred attempts. What is considered as a possible cause?