Other Parts Discussed in Thread: LMK04828

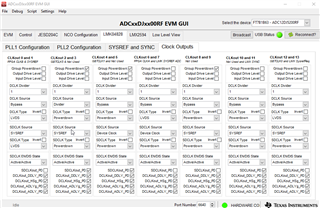

In ADC GUI,

At "EVM" tab, I do see "FPGA Reference Clock" has a division factor of 20 (default) from input provided in "#2b. External FS Selection"

For example:

#2b. External FS Selection = 4000

FPGA Reference Clock = 200

Question, Is it possible to modify this division factor in ADC GUI itself to a new number (like16 instead of 20)?

Best

Behrang