Hello,

My customer has some questions for ADS1148.

Q1.

When the new conversion is done in RDATAC mode, the converted data is automatically loaded to the shift register.

If it is done during register access by PREG command, the PREG access is interrupted by this conversion.

They would like to understand mode detail about this behavior.

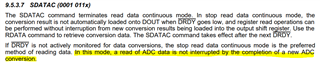

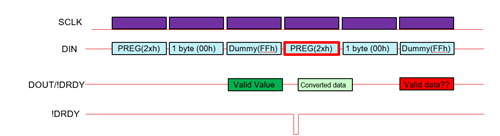

The below is the expected sequence of PREG command access.

If the new conversion is done in the middle of 1byte like the below, will the 1st bit be wrongly shifted until next CS rising?

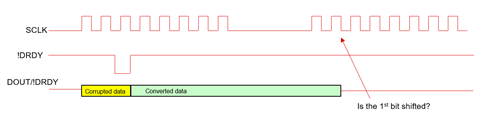

Q2

When the conversion is done during this access like the below, the returned register value is interrupted and corrupted by the conversion data.

In this case, does the 2nd PREG command still work? Is the returned value of it valid (red one)?

Q3

And the below is another case.

In this case, the new conversion is done during PREG command issuing.

Is this PREG command still valid? Is the returned value of it valid?(red one)?

Q4.

They are considering to change to SDATAC mode because the host CPU doesn’t monitor DRDY signal.

In this case, the host CPU read the data by RDATA command.

Is it OK to think there is no risk to corrupt the conversion data even though the new conversion is done during RDATA command issuing?

Regards,

Oba