Other Parts Discussed in Thread: LMK04821

Hello,

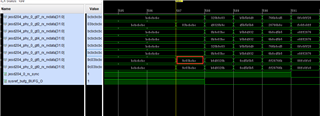

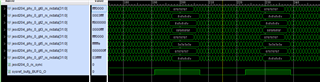

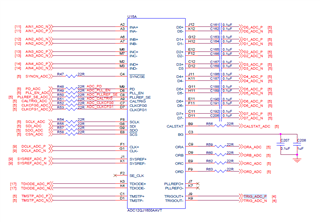

I am using adc12qj1600 ,my sample rates is 1GSPS,and use jmode0,km1=31.but I found that I can't receive k28.5 when the sync is low.the lane data I captured as below.

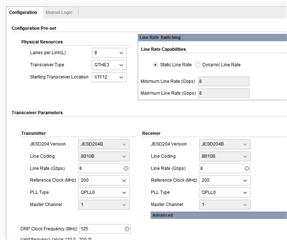

the adc's register configuration as below

{ 0x0000, 0xB0 }, //#reset registers in the ADCand master pages of the analog bank.750ns self clearing

{ 0x0270, 0 }, //Verify device initialization is completed before continuing by reading INIT_DONE until a 1 is returned.

{ 0x02c1, 0x3F }, //ALM_STATUS

{ 0x02c4, 0xFF }, //FIFO_LANE_ALM

{ 0x002B, 0x15 },

{ 0x002A, 0x02 }, //sysref_lvpecl_en = 1 dclk_lvpecl_en = 0

{ 0x0057, 0x00 }, //TRIGOUT_EN = 0

{ 0x0057, 0x01 }, //TRIGOUT_EN =0 32DIV

{ 0x0057, 0x81 }, //TRIGOUT_EN =1 32DIV

{ 0x0200, 0x00 }, //JESD_EN = 0

{ 0x0061, 0x00 }, //CAL_EN = 0

{ 0x0201, 0x00 }, //JMODE = 0

{ 0x0202, 0x1F }, //K = 32 = KM1 + 1

{ 0x0204, 0x00 }, //SYNC_SEL;offset binary;8B/10B Scrambler disabled

//

{ 0x0048, 0x00 }, //pre-emphasis,if needed

//alarm

{ 0x02c2, 0x02 }, //unmask all the alarm

{ 0x0205, 0x00 }, //test mode if needed

{ 0x0062, 0x01 }, //CAL_CFG0,disable bgos;disable os;disable bg;enable fg

{ 0x0061, 0x01 }, //CAL_EN = 1,enable the calibration state machine

{ 0x0029, 0xA0 },

{ 0x0029, 0xF6 }, //SYSREF_PROC_EN=1,SYSREF_RECV_EN=1,SYSREF_ZOOM=1,SET SYSREF_SEL

{ 0x0200, 0x01 }, //JESD_EN = 1,restart jesd link

{ 0x006c, 0x00 }, //cal_soft_trig to trigger fg

{ 0x006c, 0x01 }, //cal_soft_trig to trigger fg

{ 0x02c1, 0x3F }

could you help me to solve this problem?